# CONVERSION FROM LINEAR TO CIRCULAR POLARIZATION IN FPGA IN REAL TIME

Inaugural-Dissertation

zur Erlangung des Doktorgrades

der Mathematisch-Naturwissenschaftlichen Fakultät

der Universität zu Köln

vorgelegt von

Koyel Das

aus Kolkata, West Bengal, Indien Köln 2013

Berichterstatter:

Prof. Dr. Andreas Eckart Prof. Dr. Anton Zensus

Tag der mündlichen Prüfung: 28.06.2013

| ACKNOWLEDGEMENT                                                                     | ix   |

|-------------------------------------------------------------------------------------|------|

| CONTRIBUTIONS IN WORK                                                               | xi   |

| ZUSAMMENFASSUNG                                                                     | xiii |

| ABSTRACT                                                                            | 1    |

| 1. INTRODUCTION                                                                     | 2    |

| 1.1 Motivation to form circular polarization                                        | 2    |

| 1.2 Realization of circular polarization in analogue systems                        | 3    |

| 1.3 The digital circular polarizer project                                          |      |

| 1.4 Aims of the project                                                             | 8    |

| 2. THEORETICAL DEVELOPMENT                                                          | 9    |

| 2.1 Significance of theoretical analysis                                            | 9    |

| 2.2 Method overview.                                                                |      |

| 2.3 Instrumental phase and gain calibration                                         | 10   |

| 2.3.1 Phase equalization                                                            |      |

| 2.3.2 Gain equalization                                                             | 13   |

| 2.4 Windowing                                                                       |      |

| 2.5 Forming circular polarization                                                   |      |

| 2.6 Performance limitations                                                         |      |

| 2.7 Phase stability of the analogue receiver chain                                  |      |

| 2.8 Expected polarization purity                                                    | 19   |

| 3. PRELIMINARY TEST OF ALGORITHM                                                    |      |

| 3.1 Phase and gain equalization and windowing                                       | 20   |

| 3.1.1 Experiment to collect test data                                               |      |

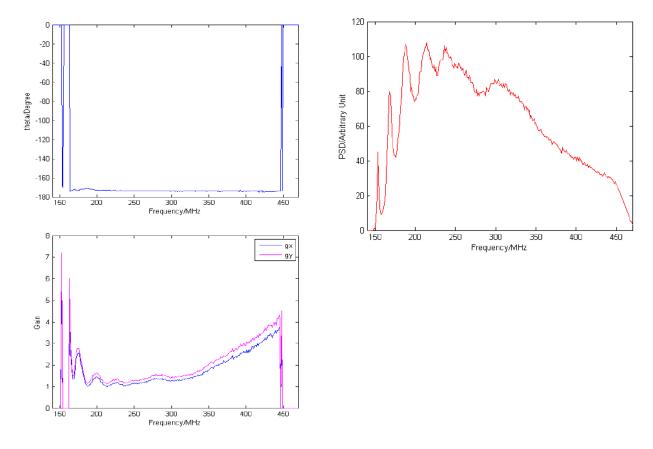

| 3.1.2 Description of spectral characteristics obtained by processing data in MATLAB |      |

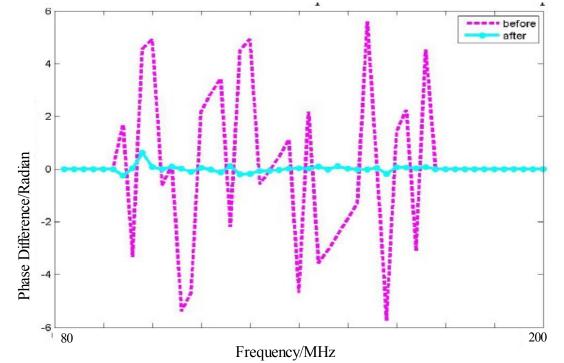

| 3.1.3 Phase equalization                                                            |      |

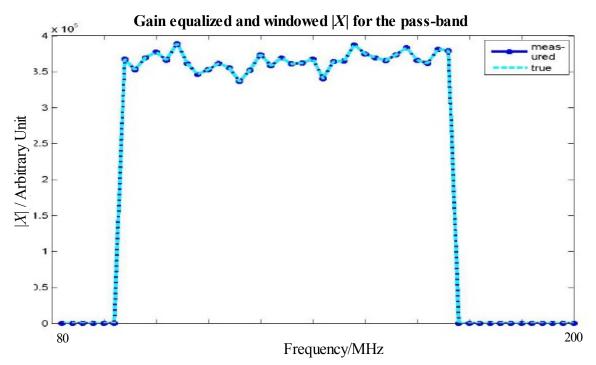

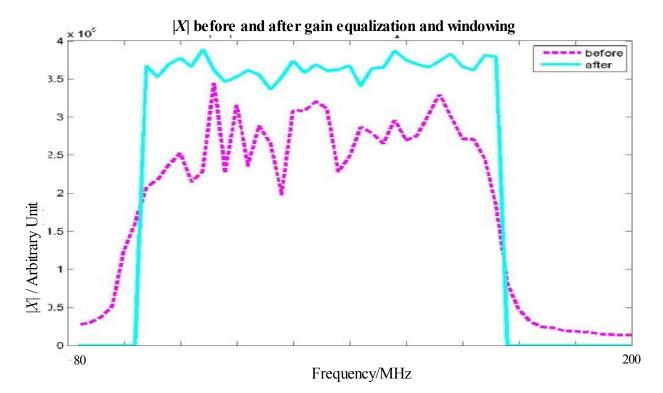

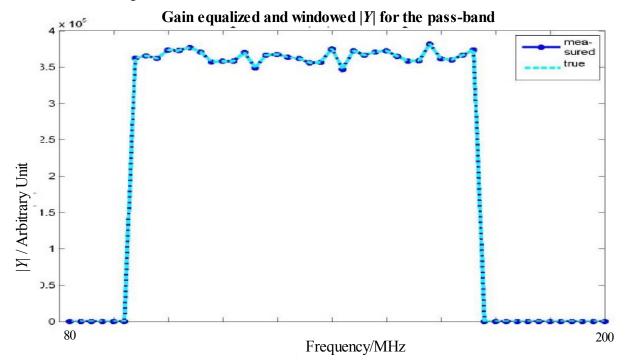

| 3.1.4 Gain equalization                                                             |      |

| 3.1.5 Windowing                                                                     |      |

| 3.2 Preliminary questions to be answered                                            |      |

| 3.3 Conclusion                                                                      |      |

| 4. IMPLEMENTATION DETAILS                                                           |      |

| 4.1 Overview of main logic blocks of the digital circular polarizer                 | 30   |

| 4.2 Conclusion.                                                                     |      |

| 5. EXPERIMENTS AND RESULTS                                                          |      |

| 5.1 Design logic verification and simulation results                                   |    |

|----------------------------------------------------------------------------------------|----|

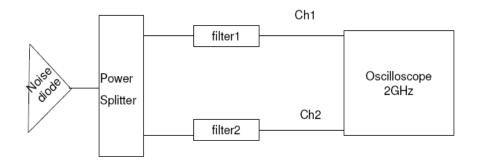

| 5.1.1 Lab setup for collecting test data                                               |    |

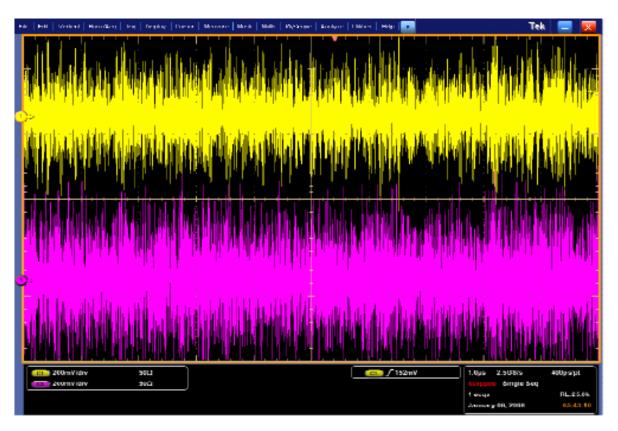

| 5.1.2 Time series obtained from the digital oscilloscope in the experiment             |    |

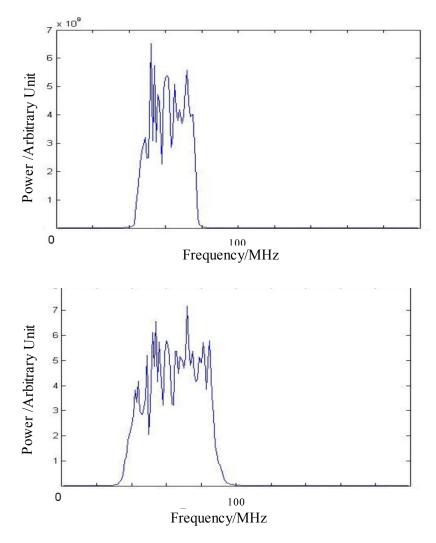

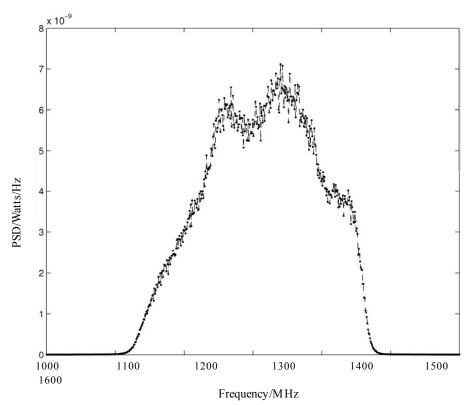

| 5.1.3 Power spectra from the two channels in the experiment                            |    |

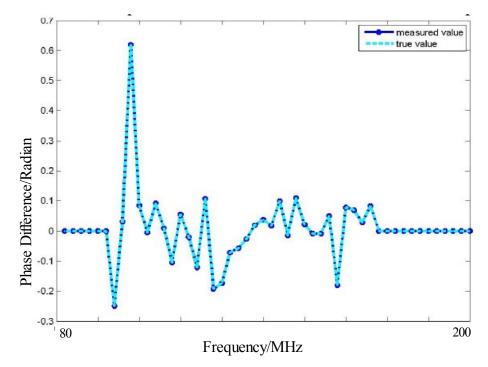

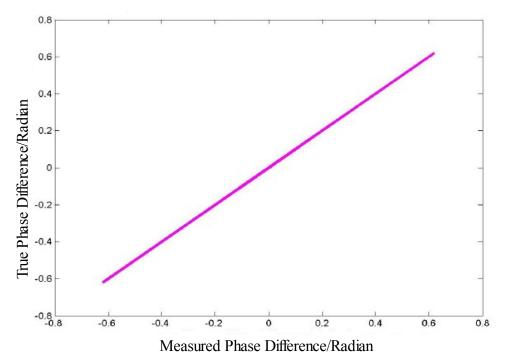

| 5.1.4 Simulation results from the design logic                                         |    |

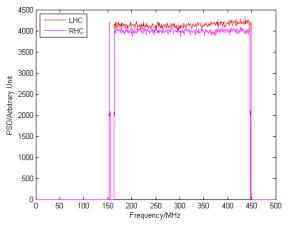

| 5.2 Verification of polarization purity                                                |    |

| 5.2.1 Signal flow through the setup                                                    |    |

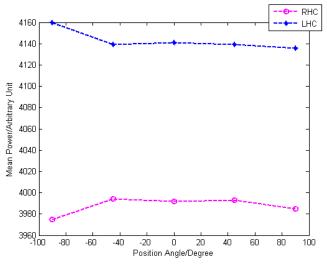

| 5.2.2 Measurement details.                                                             |    |

| 5.2.3 Results                                                                          |    |

| 5.2.4 Discussion                                                                       |    |

| 5.5 Conclusion                                                                         |    |

| 6. APPLICATIONS IN RADIO ASTRONOMY                                                     | 49 |

| 6.1 Significance of the digital circular polarizer in radio astronomy                  |    |

| 6.2 Different astronomical phenomena generating polarization                           |    |

| 6.2.1 Cyclotron and synchrotron emission                                               |    |

| 6.2.2 Plasma frequency and plasma oscillations                                         |    |

| 6.2.3 Zeeman effect                                                                    |    |

| 6.2.4 Thompson scattering.                                                             |    |

| 6.2.5 Brewster angle effects                                                           |    |

| 6.3 Depolarization effects.                                                            |    |

| 6.3.1 Depolarization due to Faraday rotation.                                          |    |

| <ul><li>6.3.2 Bandwidth depolarization.</li><li>6.3.3 Beam depolarization.</li></ul>   |    |

| 6.4 Explorations and underlying techniques requiring polarimetric observations in VLBI |    |

| 6.4.1 Magnetic field studies by the SKA                                                |    |

| 6.4.2 Studies of Sgr A*                                                                |    |

| 6.4.3 Studies of circular polarization in AGN                                          |    |

| 6.4.4 Studies of the Perseus cluster                                                   |    |

| 6.5 Conclusions.                                                                       |    |

| 7. REMAINING TOPICS OF DISCUSSION                                                      | 68 |

|                                                                                        |    |

| 7.1 Brief overview of the antenna system in radio telescopes                           |    |

| 7.2 Polarization ellipse: response of radio telescopes in ideal cases                  |    |

| 7.2.1 Retrieving linear polarization in the sky from elliptical response of antenna    |    |

| 7.3 Polarization ellipse: response from imperfectly oriented dipole elements           | 73 |

| 7.4 Analysis of the ellipse in the experiment described in section 5.2.                |    |

| 7.5 Effects of D-term in the received voltage by the crossed dipole                    |    |

| 7.5.1 Discussion on relation between circular D-terms and ellipticity                  |    |

| 7.6 Conclusion                                                                         | /6 |

| FUTURE WORK                                                                            | 77 |

| APPENDICES:                                                                            |    |

| APPENDIX A: BASIC POLARIZATION DERIVATIONS                                             |    |

| APPENDIX B: DESIGN AND CODE DESCRIPTION OF LOGIC BLOCKS O<br>4 |     |

|----------------------------------------------------------------|-----|

| APPENDIX C: VHDL CODES OF SELECTED MODULES FROM APPENDIX B     | 127 |

| REFERENCES                                                     |     |

| ERKLÄRUNG                                                      |     |

| DECLARATION                                                    | 156 |

| LEBENSLAUF                                                     | 157 |

# ix

# ACKNOWLEDGEMENT

The successful completion of this PhD thesis has entailed a lot of support and cooperation from the people who are involved directly or indirectly in my PhD project and also sometimes from the people who are not involved in the project at all. First of all, I would like to thank my supervisor, Dr. Alan Roy of MPIFR, without whose cooperation, the project wouldn't have been completed. The project's basic algorithm, which came from him, seemed to be simple in the beginning but later I and my supervisor realized the length of the project taking all technical challenges into account. Alan solved all technical problems that were causing road block in the commencement of the project. He has provided the best supervision along with being an excellent discussing partner. He has organized regular thesis committee meetings to keep everyone, involved in the thesis, informed about the work progress and also to plan timing of the remaining work. Since there are too many contributions, in work, on his part, I will include a separate paragraph on contributions in work towards my PhD thesis. I would also want to thank my official supervisors, Prof. Dr. Andreas Eckart of University of Cologne and Prof. Dr. Anton Zensus of MPIFR for being there in my PhD related matters. I simultaneously thank IMPRS for funding my PhD projects.

There were many difficult times during the commencement of my PhD and all three of the above mentioned people have supported me in one way or the other so that the project was completed successfully. Andreas Eckart has attended all my thesis committee meetings and his presence in all those meetings enhanced my confidence about my performance in the project. I am thankful to Andreas Eckart for taking the effort of traveling from Cologne to Bonn to attend my thesis committee meetings. I was able to be fully optimistic towards completion of my thesis due to the presence of Andreas Eckart in my PhD related matters.

Anton Zensus has supported my project by being there towards completion of the project. He has also attended thesis committee meetings in the beginning. I thank Anton Zensus and other members of IMPRS for selecting me as a PhD student. I am thankful to Anton Zensus for providing me an interrupt in work after my mother's demise as it was really necessary when I lost my most beloved one suddenly in the mean time of my PhD; my mother's death was the most disastrous happening for me that could happen. Anton Zensus provided financial support for my stay in Bonn during the interruption period, which was extremely kind.

Due to the support from Alan Roy, Andreas Eckart and Anton Zensus, I could proceed with my thesis writing with ease. My PhD work has helped me to keep my mind away from the feeling of the loss of my mother and also helped me to cope with the situation; thanks to Alan for discussing work with me continuously throughout my PhD, which kept my mind in the work only.

After the above mentioned three people who are involved in my thesis, I would thank Dr. Reinhard Keller, also involved in my project, for organizing the experiment in my project through members of the RF lab and attending my thesis committee meetings sometimes; I would thank Thomas Berenz of RF lab for doing the setup in the experiment of my project as per the guidance from Alan. I am extremely thankful to Thomas Berenz for translating the abstract of this thesis to German language as required by the university of Cologne. Then I thank Prof. Dr. Brian Corey for taking interest in my

thesis and also for going through the first draft of this thesis. Then I thank Dr. Dorothea Samtleben who reviewed my paper before publication as my internal referee. Next I would thank Dr. Gino Tuccari, also involved in my project, for discussing his DBBC project and this project with me. Next I would thank Dr. Stefan Hochgürtel of the digital lab for answering a few of my questions in the project. I would thank Prof. Bernd Klein for attending my thesis committee meetings at crucial times. I would also thank Prof. Dr. Rajaram Nityananda for answering three questions and Prof. S. Ananthakrishnan. Also thanks to Prof. Dr. John Black and Dr. Gary Smith Jonforsen for their encouragement. Also thanks to my father and sister for their support. Also thanks to Simon Pott. Finally, I dedicate my PhD thesis to Dr. Alan Roy, Prof. Dr. Andreas Eckart and Prof. Dr. Anton Zensus for keeping up their support towards completion of my PhD and to my mother who had given her whole life for my education.

# **CONTRIBUTIONS IN WORK**

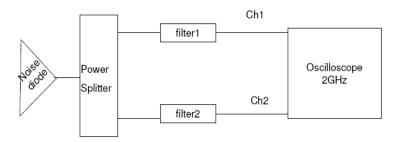

It took a lot of effort on my part and on my supervisor's, Dr. Alan Roy's part to finish this project successfully. My supervisor was always there to solve whenever there was a problem in my project. He has collaborated with me in the best possible manner towards completion of this PhD thesis. The effort started with the verification and theoretical justification of the basic algorithm he laid out to me regarding the digital circular polarizer. I discussed thoroughly with Alan each and every stage of signal processing to explore the exact steps of signal processing towards formation of pure circular polarization from two orthogonal linear polarization inputs. I laid out a theoretical justification of his algorithm and he went through that and we discussed thoroughly each and every step of the theory. We collected data from an experiment described in section 3.1.1 and 5.1 of this thesis for me to check the steps of the algorithm. I also played the main role in defining the data collection method in this experiment. I as per Alan's suggestion simulated the logic and checked the correctness of the algorithm at each stage and also showed the results from each stage to Alan.

After the theoretical justification was complete, I as per Alan's suggestion proceeded towards firmware development where first I had to design logic blocks to convert from two orthogonal linear polarization to two hands of circular polarization in real time. After design of each block, corresponding VHDL code was written by me. Alan discussed with me during block design suggesting methods sometimes, which I implemented. Stefan Hochgürtel of the digital lab also discussed with me sometimes about the block design, which was also useful. After writing the codes for different logic blocks and verifying those in simulation, I needed to connect all the blocks together to have the digital circular polarizer ready for testing. I also tested the the implementation of the individual blocks in Xilinx ISE with timing constraints met so that there is no problem later on in implementing the connected logic. In the design I used many logic blocks developed by Xilinx and while connecting them I faced difficulties since I was not getting the correct simulation results for one of the Xilinx logic blocks. Alan solved this problem by corresponding with Xilinx and correcting the technical problems, which were causing the road block. Alan also solved other many more technical problems that were snagging the project.

After I connected all the logic blocks together, I tested the connected logic in simulation by using self generated data streams. After I saw the simulation results were correct, I reported to Alan and we decided to test first the complete design using the same data obtained from the experiment described in section 3.1.1 and 5.1 of this thesis where I took the leading role. I ran the simulation by using that data stream as the input to the digital circular polarizer and checked the correctness of the design in each stage. I showed Alan the simulation results from each stage and we discussed the observed facts with Alan supervising me in observing details. We observed together the correctness of the design. The results that validated the design are depicted in section 5.1.4 of this thesis. After we were sure that the design logic was correct, we decided to perform the second experiment (given in section 5.2 of this thesis) proposed in our theory to validate the algorithm finally.

We talked to Reinhard Keller for arrangement of the setup for the experiment. Reinhard Keller and Thomas Berenz of the RF lab did the setup for us as per Alan's guidance and I noticed all the details of the experiment along with discussing with Alan from time to time as Alan guided the experiment. We took some measurements. After the data were collected in the way described section 5.2.1 of this thesis, we started arrangements for processing the data using the firmware running in a simulator for verification prior to running the firmware in hardware in the FPGA. The data set was huge and very high computing power was needed along with an advanced simulation tool (ModelSim). Alan purchased an advanced simulation tool through IMPRS for me that can handle big designs and that run

much much faster than the normal simulation tools. I broke the design into two parts; each of the two parts was replicated to be fed simultaneously with a part of the data collected to the simulator; all the parts of the collected data for all the parts of the replicated designs comprised of equal number of data points. I ran the simulation, which required a few days. The details of simulation is given in section 5.2.2 of this thesis. After simulation was complete I reported to Alan and we started analyzing the results with Alan supervising me in finding details. Most of the times during analysis I learned many details from Alan and accepted his reasoning after thinking thoroughly through them. The observed facts are described under section 5.2.3 of this thesis.

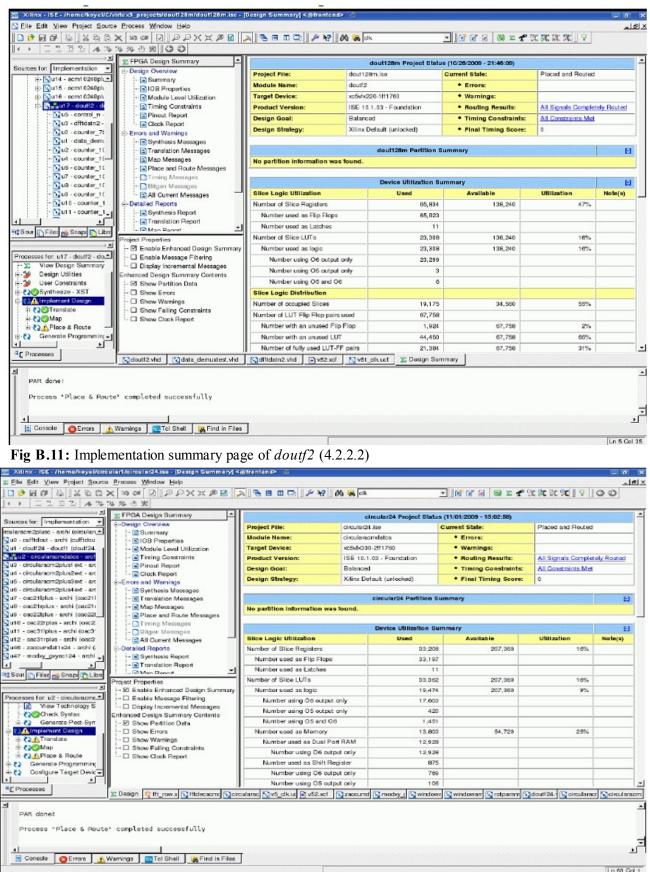

Then we were sure of the correctness of the algorithm and of the instrument and I proceeded towards implementing the whole logic in Xilinx ISE taking all constraints like the timing into account. I truncated bits in stages of the logic as per Alan's supervision and implemented the whole design with all constraints met in Xilinx; then only connecting the design to DBBC and loading of the design in FPGAs were remaining. The information on implementation of different parts of the design is given in section 4.3 of this thesis. The total time taken to design the digital circular polarizer addressing all technical difficulties was nearly one and a half years. Thanks to Alan as without his help the technical problems couldn't be solved.

We decided to publish the results and it took around three to four months in writing and polishing the paper. I wrote a first draft of the paper and gave that to Alan for corrections. Alan corrected the paper and gave me modifications at several places in the paper until he found the paper was ready for submission. He also included about two pages initially written by him with me discussing the detail and doing minor modification at one place. The experiment described in the paper (second experiment) and its results were written by us with Alan adding details about the experiment as he was the one who took the leading role in this experiment. He also added other details at several places in the paper. Along with reviewing our paper thoroughly and suggesting changes, he also suggested language modifications, which I followed. He also contributed towards polishing the paper and I followed his suggestions. Dorothea Sambtleben, my internal referee, helped in polishing the paper too. Gino Tuccari and Reinhard Keller also reviewed the paper. After the paper was published, I and Alan tried to see if we could get FPGA boards (DBBC boards) for loading the firmware but they were unavailable and hence we couldn't proceed further.

Next came thesis writing; Alan taught me the proper style of writing a thesis by teaching the guidelines that should be followed like the word limits. He also showed me the writing style in the first chapter where I had just written the points only properly in the beginning; he gave modifications again and again and I modified accordingly until it reached the level of satisfaction and I got the idea about how to write the later chapters and I followed the same way of writing in the rest of the chapters. I have then written the rest of the chapters in a way to entail minimum effort on Alan's part in doing corrections. He also gave me literature to read for the first and fifth chapters. He has done a thorough correction of all the chapters and I have implemented all his corrections. I am thankful to Alan for being there as a strong support while I was writing the thesis. Even though I have written the whole thesis, Alan's corrections were necessary and his support for completing the thesis was a source of moral strength to me. Finally, I am grateful to Alan Roy, Andreas Eckart and Anton Zensus for keeping positive attitude about completion of my thesis from the time when nothing were written up; it gave a lot of support to me on the basis of which I could start writing it up. I expect that the developed firmware gets implemented successfully in future to be used in radio telescopes.

#### ZUSAMMENFASSUNG

Zukünftige Radioastronomische Empfänger werden über einen erweiterten Frequenzbereich und damit auch eine höhere Bandbreite (Oktave) verfügen, um die Empfindlichkeit zu steigern und mehr Flexibilität bei der Auswahl des Frequenzspektrums zu haben. Dies stellt hohe Anforderungen an das Design eines analogen Frontends. Um bessere Polarisationseigenschaften zu bekommen, ist eine flacher Phasenverlauf über immer größere Bandbreiten nötig, was am einfachsten mit digitalen Methoden zu erreichen ist. Hier besitzt man die Möglichkeit eine zirkulare Polarisation mit perfekter Polarisationsverteilung über eine vorgegebenen Bandbreite zu formen, da mit digitalen Mitteln einfacher eine quadratur Phasenverschiebung zu erzeugen ist. In analogen Systemen ist die nötige Phasenverschiebung nicht exakt, sobald man von dem Frequenzpunkt abweicht für den das System entworfen wurde. Im Gegensatz dazu besteht bei digitalen Systemen die Möglichkeit, die exakte Phasenverschiebung durch Verrechnung der Signalvektroren jedes einzelnen Frequenzpunktes innerhalb des Frequenzbandes zu erzeugen. Daraus resultiert dann eine perfekte quadratur Phasenverschiebung innerhalb des kompletten Bandes. Der schnelle Fortschritt bei Field Programmable Gate Arrays (FPGA) bringt neben der nötigen Rechenleistung, einem günstigen Preis und der Portierbarkeit auch die Möglichkeit zur einfachen und schnellen Rekonfiguration des Systems, wodurch das Formen einer zirkularen Polarisation mit digitalen Mitteln auch praktisch sinnvoll wird. Dieses System kann dann für breitbandige Polarisationsmessung genutzt werden.

Zirkulare Polarisation wird aus Geometrischen- und Stabilitätsgründen bei der Radiointerferometrie mit sehr langen Basislängen (very long baseline interferometry, VLBI) genutzt. VLBI wird häufig bei der Untersuchung der Polarisation von Radiowellen verwendet. Die Polarisation dieser Wellen wird durch Syncrotron Effekte, Zeeman Effekte innerhalb von Atomen und Molekülen, Zyklotron Strahlung und Plasma Schwingungen in der solaren Atmosphäre hervorgerufen. Außerdem findet VLBI Anwendung bei Methoden der Synthese der Rotationsmessung, welche verwendet werden kann um die magnetische Feldstärke zu ermitteln. Weiterhin kann durch Beobachtung verschiedener Wellenlängen die Richtung des magnetischen Feldes bestimmt werden. Daher würde ein digital arbeitender Polarisator eine Vielzahl von Anwendungen in VLBI Systemen finden.

In dieser Arbeit untersuche ich die Effizienz eines digitalen zirkularen Polarisators. Wir entwarfen einen digitalen zikularen Polarisator in dem die Zwischenfrequenzsignale eines Empfängers mit ursprünglich linearer Polarisation abgetastet wurden. Diese wurden nach dem Abtasten in eine zirkulare Polarisation gewandelt. Die frequenzabhängige Phasen- und Amplitudendifferenz des Systems wurde mit Hilfe eines zugeführten Rauschsignals bestimmt. Dieses wurde auf beide linearen Polarisationen gegeben um die Übertragungsfunktion der beiden Polarisationskanäle abzugleichen. Dieser Abgleich wurde mit 512 Frequenzpunkten über eine Bandbreite von 500 MHz durchgeführt. Die zirkulare Polarisation wurde durch eine quadratur Phasenverschiebung und anschließende Summation des Signale erzeugt. Hierbei erzeugten wir über das ganze Band eine Polarisationsreinheit von -58 dB, was einem D-Wert von 0.0012 entspricht. Dieses D-Wert eine Obergrenze

Diese Technik ermöglicht die Entwicklung eines zirkularen Polarisators für VLBI, der mit einem breitbandigen radioastronomischen Empfänger mit linearer Polarisation arbeiten kann

#### ABSTRACT

Radio astronomical receivers are now expanding their frequency range to cover large (octave) fractional bandwidths for sensitivity and spectral flexibility, which makes the design of good analogue circular polarizers challenging. Better polarization purity requires a flatter phase response over increasingly wide bandwidth, which is most easily achieved with digital techniques. They offer the ability to form circular polarization with perfect polarization purity over arbitrarily wide fractional bandwidths, due to the ease of introducing a perfect quadrature phase shift. In analogue systems the quadrature phase shift is not accurate in the regions away from the design point or frequency. In digital systems on the contrary, it is possible to introduce the exact quadrature phase shift vectorially to each frequency point in the band thus producing a perfect quadrature phase shift throughout the band. Further, the rapid improvements in field programmable gate arrays provide the high processing power, low cost, portability and reconfigurability needed to make practical the implementation of the formation of circular polarization digitally. It will be possible to carry out broadband polarization observations.

Circular polarization is used in very long baseline interferometry (VLBI) due to geometrical and stability considerations. VLBI is often used to explore polarization of radio emission, which often occurs due to synchrotron mechanism, Zeeman effect in atoms and molecules, cyclotron radiation and plasma oscillations in the solar atmosphere. Also VLBI finds application in methods like rotation measure synthesis that can be used to find the magnetic field strength and whose multiwavelength observations determine the direction of magnetic field. So a digital circular polarizer would find a considerable application in VLBI systems.

Here I explore the performance of a circular polarizer implemented with digital techniques. I designed a digital circular polarizer in which the intermediate frequency signals from a receiver with native linear polarizations were sampled and converted to circular polarization. The frequency-dependent instrumental phase difference and gain scaling factors were determined using an injected noise signal and applied to the two linear polarizations to equalize the transfer characteristics of the two polarization channels. This equalization was performed in 512 frequency channels over a 500 MHz bandwidth. Circular polarization was formed by quadrature phase shifting and summing the equalized linear polarization signals. I obtained polarization purity of -58 dB corresponding to a D-term of 0.0012 over the whole bandwidth. This value of D-term is an upper limit.

This technique enables construction of broad-band radio astronomy receivers with native linear polarization to form circular polarization for VLBI.

# **CHAPTER 1**

## **INTRODUCTION**

In this chapter I provide the initial motivation to form circular polarization digitally in real time, which when implemented in practice would allow new receivers to have native linear polarization for broad frequency coverage. I simultaneously discuss the realization of circular polarization in analogue systems giving examples. Then I discuss the problem of obtaining a perfect 90° phase shift required to be introduced to the phase of one of the two linear polarizations for the formation of circular polarization in existing analogue systems providing an example from Effelsberg radio telescope and finally I describe our developed digital circular polarizer and provide the aims of our project solving the problems.

#### 1.1 Motivation to form circular polarization

Circular polarizers play important roles in modern communication systems including those in radio astronomy. To obtain higher sensitivity and frequency coverage for spectral line observations, the radio antennas are moving to broad-band feeds and extremely broad bands are most easily realized with linearly polarized feeds due to the difficulty of producing 90° phase shift accurately over wide bandwidth. However, circular polarization is simplest for the application of very long baseline interferometry (VLBI), which enables astronomical sources to be resolved with sub-milliarcsecond synthesized beam widths, since linear dipoles do not generally remain parallel to each other in a global array due to different parallactic angles at different stations when observing the same source, causing loss of coherence in the cross-correlation products formed between stations. That loss could be recovered were one to compute also the cross-polarization cross correlation products to retain all information (doubling the correlator power needed), or one could rotate the receiver packages at each station to keep the dipoles parallel (requiring mechanical rotators). In contrast, use of circular polarization causes the parallactic angle differences between stations to add a simple phase rotation angle to the measured visibility, which can be predicted from the known observation geometry and subtracted in post-processing.

Circular polarizers with broad bandwidths have been realized in the past with a number of methods. Most common are as follows: 1) The septum polarizer originally designed by Davis et. al. (1967) and modified by Chen & Tsandoulas (1973); they introduced steps in the septum for better performance in terms of axial ratio and input port isolation. 2) Boifot et. al. (1990) is the origin of Boifot junction; they presented a broadband OMT (orthomode transducer used to couple out the two linear polarizations from waveguide into coax); an isolation better than 50 dB and a return loss less than -20 dB was achieved. 3) Linear quad-ridge OMT followed by a 90° hybrid junction or preceded by a corrugated waveguide phase shifter (Simmons 1955); these convert the linears into circular; Simmons provided analytical and experimental results of producing a differential 90° phase shift produced by phase delay and phase advance of two fundamental modes; it is done by loading the transmission line equivalent circuit of a rectangular or square waveguide with capacitance and inductance respectively; Srikant (1997) explains that corrugated phase shifter, which is not a polarizer on its own, can be used in conjunction with an OMT to form circular.

All are analogue techniques and produce a perfect 90° phase shift and hence perfect polarization purity

at only one, two, or three frequencies and the phase errors grow larger at frequencies away from those design points, which ultimately limits the bandwidth of the devices. In contrast, digital techniques offer the possibility to produce an accurate 90° phase shift over broad bandwidths, but this potential has not yet been fully developed. One example is the Westerbork synthesis radio telescope, which converts native linear polarization to circular polarization by a combination of analogue and digital techniques for VLBI. During down conversion of the orthogonal linear signals, the 90° shift is added to the (analogue) LO for one polarization. After analogue-to-digital conversion, the (2 bit) signals are summed and differenced to form circular polarization, with a weight that corrects for the average receiver gain differences. The weights are determined by a separate measurement using a calibration noise source in each frontend and are updated every 10 s. This system operates on a bandwidth of 20 MHz, yielding one phase and amplitude correction for each 20 MHz of bandwidth (Boss 2007, private communication). The Westerbork system uses the pre-existing correlator and analogue phase rotation in the LO system, but most VLBI stations lack this equipment and so another, more general, solution is needed.

# 1.2 Realization of circular polarization in analogue systems

Conventionally, analogue circular polarizers are used to obtain circular polarization and all of them use some technique to impart a 90° phase shift between orthogonal linear field components.

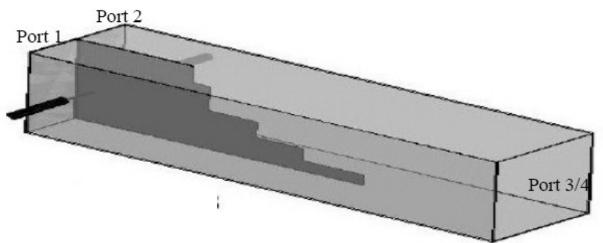

An example is the very compact septum polarizer first devised by Davis et al. (1967). They used a sloping septum to obtain the polarization components and their phase relationships. Later Chen & Tsandoulas (1973) introduced steps in the septum to avoid reflection off the discontinuity that the septum creates in the waveguide. Here I provide an example of the septum polarizer described by Wade (2003), which is realized with a rectangular input waveguide containing both circuit input ports and two physically separated waveguide output ports that are physically quadratic (for our application). Fig.1.1 illustrates the septum polarizer. A septum polarizer can be considered as an equivalent four port

**Fig. 1.1**: Septum polarizer with four ports. Ports 3 and 4 are present in the same waveguide port and is only distinguishable conceptually. Ports 1 and 2 are physically separated (Wade 2003). The radiation enters port 3 and port 4 through a horn antenna in quadrature i.e there is a quadrature phase difference between the two circular polarization components and the two linear polarizations are obtained from port 1 and port 2. The thick black lines at the left side of the polarizer are output dipoles to extract the linear polarizations coming out. This septum polarizer responds to circular polarization in the sky and hence is relevant to our application.

microwave circuit. The two input ports (3,4), which are only conceptually distinguisable, are contained in the same physical rectangular waveguide port and the two output ports (1,2) are physically separated with a fin. Let us consider a circularly polarized wave comprising of two polarization components with a 90° phase difference, entering the aperture (ports 3, 4). One of the components is parallel to the septum and the other is perpendicular to the septum. The septum divides the parallel component equally, which passes to the two rectangular output waveguides. The septum changes the cutoff frequency of the perpendicular component thereby shortening the wavelength of the perpendicular component. This means that the section of the waveguide containing the septum is electrically longer for the perpendicular component as compared to the parallel component. A path difference of  $\lambda/4$  will render the vertical and horizontal component to be in phase at the output. However, there can still be phase differences as the band deviates from the centre frequency for which the septum polarizer is manufactured. The two output ports are isolated from each other. Constructive or destructive interference of the field components occurs at either side depending on the sense of circular polarization. The operating frequency is near the waveguide cutoff which leads to difference in electrical lengths between the two components. A circular waveguide can be used in place of the rectangular waveguide in Fig. 1.1 as the circular waveguide input is very useful especially while receiving signals from circular waveguide horn antennas having both LHC and RHC polarizations.

However, it is very difficult to obtain good isolation between the two orthogonal components. Fig. 1.2 illustrates an orthomode transducer developed by Dunning (2002). Good isolation prevents leakage of

Fig. 1.2: Double ridged orthomode transducer by Dunning (2002). The two orthogonal linear components enter the square waveguide through the top end. One component, which is parallel to the plane of the ridges gets concentrated between the ridges at the center of the waveguide and is removed by a coax through one of the fins in the square waveguide. The other component reaches the square to rectangular transition and is removed by another coax through a fin in the rectangular waveguide. This orthomode transducer provides verv good isolation between two polarizations.

one polarization component into another thereby facilitating the production of pure circular polarization without any ellipticity. The orthomode transducer developed by Dunning has good isolation between two polarizations and low insertion loss suitable for broad band radio astronomy receivers. It takes the two orthogonal field components excited at one common port and separates them. In that double ridged OMT, one polarization is concentrated between the ridges at the centre of the square waveguide and is removed by a coax inserted through one of the fins in that square waveguide. The other polarization is unaffected by the ridges and reaches a square to rectangular waveguide transition from where it is removed by another coax, which is inserted through one of the fins in the rectangular guide. A 90° hybrid could be connected to the output coax ports in order to convert to circular polarization. The excellent OMT developed by Dunning has achieved isolation better than 50 dB between ports and an insertion loss better than 0.3 dB for a 47 % fractional bandwidth.

Now, I will proceed to demostrate the difficulty in producing a quadrature phase shift between two orthogonal linear polarizations to obtain the circular polarization in existing analogue systems.

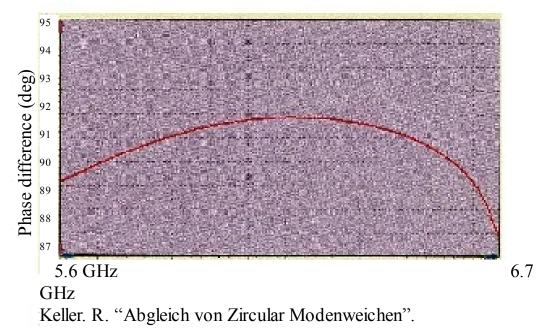

It is extremely difficult to obtain perfect 90° phase shifts using analogue polarizers. The quadrature phase shift is perfect only near the centre frequency. Fig. 1.3 shows the typical phase difference between the two orthogonal polarization components as measured for the polarizer in the 5 cm receiver at Effelsberg. The plot is provided to me by Alan Roy.

Fig. 1.3 : Phase difference between two orthogonal polarization components for the polarizer in the 5 cm receiver at Effelsberg. The phase difference varies across the band from 88.2° at the lower edge to 85.8° at the upper edge. It is around 90.9° near the centre frequency, 90° was chosen to be at two frequencies in order to distribute the errors and broaden the bandwidth. It is very difficult to obtain exact 90° phase difference over broad bands.

This is the phase difference between the two orthogonal components of the circular polarization to which the polarizer responds in the receiving system. It can be seen from the plot that the phase difference is around 90° at two frequencies for which the polarizer was optimized and it deviates as we move away in frequency towards the edges. The phase difference varies from 90.9° at the centre to

88.2° at the lower band edge and to 85.8° at the upper band edge. Hence it is very difficult to obtain an exact 90° phase shift over broad bands.

After discussing the analogue techniques I will now demostrate our digital technique to produce circular polarization from two linear orthogonal polarization components.

# 1.3 The digital circular polarizer project

In this project I have tried to form an exact 90° phase shift for a 200 % fractional bandwidth. I have tested that the polarizer works for 97 % fractional bandwidth. The aim was to obtain pure circular polarizations correcting all system imperfections leading to perfect 90° phase shift, which is one of the challenging aims of modern circular polarizers. This project is based on the idea of Alan Roy that if the circular polarization is formed in the digital domain then it might be possible to obtain flatter phase response over broad bands. I explored this by performing some initial simulations on test data before proceeding towards actual instrument development.

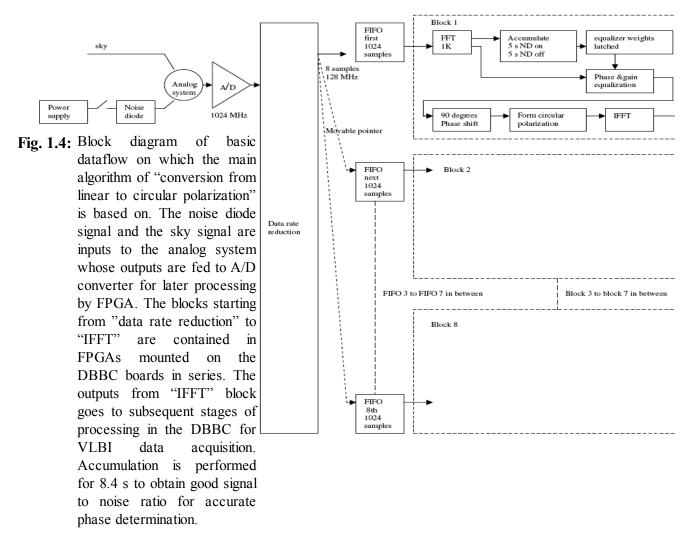

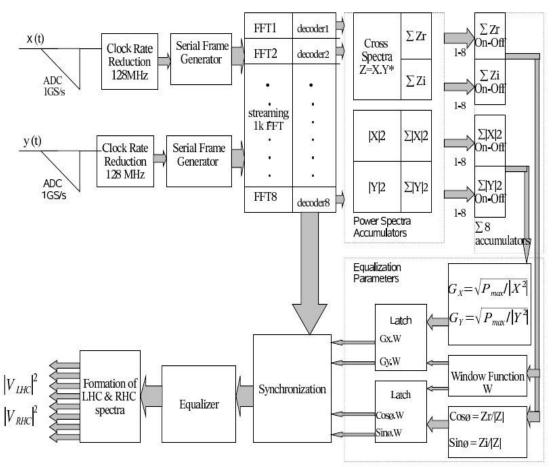

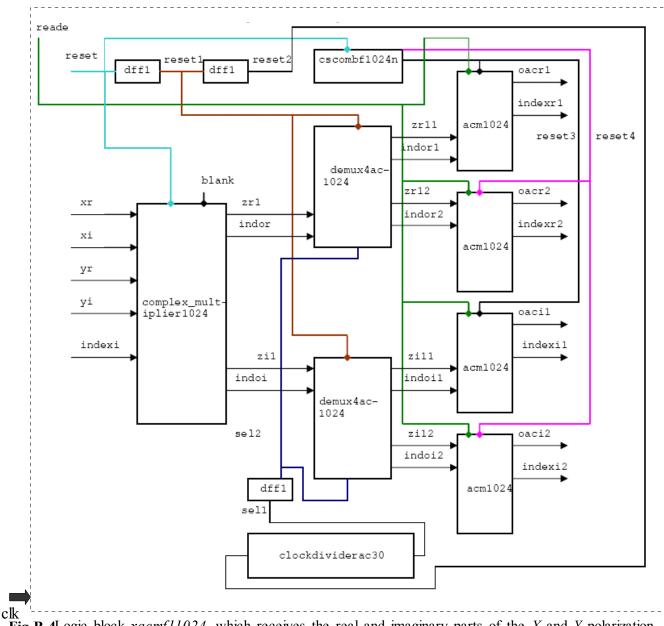

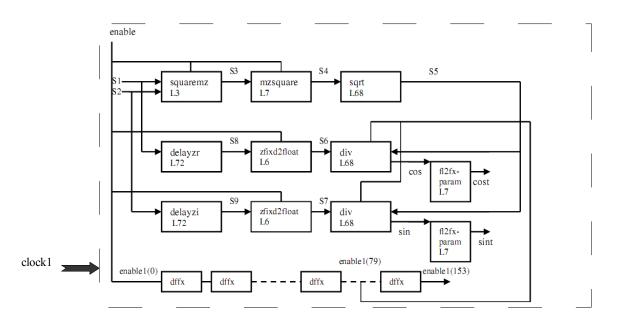

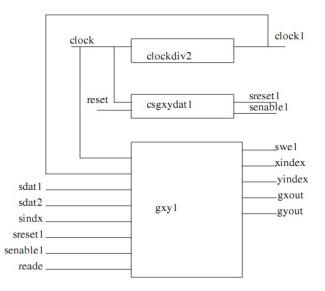

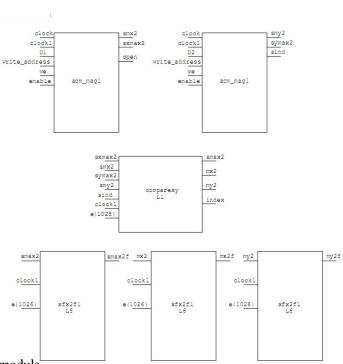

I have developed a self-contained digital processing system in which the correlator, channel equalization, phase rotation, gain scaling, quadrature phase shift and summation to form circular polarization are contained in a stand-alone unit. I and Alan arrived at the basic data flow shown in fig. 1.4. It accepts two intermediate frequency inputs with orthogonal linearly polarized signals, each of 500 MHz bandwidth and subdivides the band down to 1 MHz resolution. In each 1 MHz piece it measures the phase and amplitude differences between the orthogonally polarized channels using a

calibration noise source in the front end that is common to both polarizations. It then uses those measurements to equalize the channel phases and amplitudes during observations. After equalization it introduces an ideal 90° phase shift into one polarization channel and forms sum and difference outputs that respond to orthogonal circular polarizations at the input. I perform an FFT to process the data in frequency domain for the simplicity to work in that domain.

We decided to use FPGAs since they have high computing power and are reconfigurable and portable. I took sampled time domain data and processed them in MATLAB as a quick preliminary test of the idea behind it, which came from my supervisor, before exploring the algorithms in detail. The results are shown later in the thesis. At this point I verified that the principle was sound and that the implementation could begin. The data flow shown in the figure is for each polarization state.

The signal received by the dipole is sampled using an analogue to digital (A/D) converter for later processing in FPGAs (DBBC boards, which are described later in this chapter, connected in series). Each eight consecutive samples coming in series at 1024 MHz are converted to eight parallel samples at 128 MHz by the data rate reduction block. There are eight FIFOs running in parallel to receive data from the data rate reduction block at the rate of 128 MHz to handle the speed of 1024 MHz. Until this point the blocks duplicate for the other polarization state.

After the above mentioned logic there are eight blocks, "block 1" to "block 8" each of which are connected to a pair of FIFOs only one of which is shown in the figure. The logic blocks inside these blocks are shown in the figure. The FFT performs a Fourier transform on the input polarizations which are fed to the two input channels of the FFT (I perform an FFT of 1024 samples to produce spectra with 1 MHz channel spacing and the whole algorithm involves computation of time separated spectra in the frequency domain) and the outputs are decoded and fed to power spectra accumulators and cross power spectra accumulators. The accumulators run for 8.4 s with noise diode, which is used as a calibration are carried out in separate accumulators.

In the next block the phase and gain scaling factors are determined and latched to be read out during equalization. After equalization of the FFT outputs by the block "phase and gain equalization", one of the two polarizations is 90° phase shifted and the circular power spectra are formed in the next block, which are then converted to time domain to feed later stages of DBBC for VLBI data acquisition. There is a noise diode control signal generated inside the FPGA (not shown in the figure). It goes high at the same time when the on-state accumulator is enabled and it goes low when the off-state accumulator is enabled. This signal is brought out of the FPGA and it controls the TTL (transistor-transistor logic) signal that controls the switching on and switching off of the noise diode signal.

After discussing the basic data flow I will now demonstrate the motivation to implement this design in FPGAs rather than using the conventional orthomode transducers to convert linear polarization to circular polarization.

Digital systems offer the ability to process continuous data in real time implementing automatic data processing algorithms. Data transmitted digitally are more resistant to external interference and hence digital devices supersede analogue counterparts at least where speed and signal purity are matters of concern. With the advent of logic devices like ASICs and FPGAs, it is possible to implement many complex algorithms, which would have been impossible otherwise and they also offer the user ease of replication compared to analogue systems. For these reasons our system to produce circular polarization n generates almost perfect orthogonal field components in real time.

I have three options for implementation in the digital domain: 1) Software implementation, 2) ASIC (application specific integrated circuits) and 3) FPGA (field programmable gate arrays). Practical software implementation would require huge computing power to process the data in real time and it is difficult to have such computing power at the VLBI stations where I have aimed to form the circular polarization in real time. ASICs cannot be reconfigured and reconfiguration can be necessary in the future to increase bandwidth. ASICs also have large development and fabrication costs and for our application FPGAs have lower cost. Thus the most obvious option was to use FPGAs. The implementation in Xilinx software is complete with all timing constraints met and hence all the technical difficulties have been addressed. Also FPGA-based VLBI data acquisition systems, such as the Digital Base-Band Converter (DBBC, Tuccari 2004) are being deployed in many radio telescopes. The DBBC is a signal conditioning device used in VLBI observations and has ADCs and FPGAs for digital downconversion, digital filtering, and outputs 2 bit depth to VLBI recorders. It has the capability to sample at a rate of 1024 MHz clock rate. It produces eight parallel digital samples each of eight bits as intermediate output signals internal to the DBBC that are contained in eight buses each running at a clock rate of 128 MHz. These eight intermediate signals are the inputs of our project, which will also be placed inside the DBBC.

I have truncated bits in stages of the data flow in order to fit it inside the DBBC, as per Alan's Guidance, which has a predefined number of input output pins. A new DBBC board is being developed which would have a Virtex 7 mounted on it. So we have decided to implement the design in Virtex 7, which would encompass the bigger parts of the design and fewer number of FPGAs would be required. Thus it is best to use the DBBC with Virtex 7 as then the whole logic inside the FPGA will be utilized efficiently, that is, less approximations will be required since number of logic elements are much more than in Virtex 5 on which the design is already tested.

# 1.4 Aims of the project

This thesis acquaints the reader with the theory and derivation for obtaining instrumental phase and gain correction factors and applying them to the two received orthogonal linear polarizations to form phase and gain calibrated left hand circular (LHC) and right hand circular (RHC) polarizations. It explores limitations of system performance due to the most influential factors, which are the D-terms and receiver instabilities and explores the requirement for periodic recalibration to remove their detrimental effects on polarization purity. It also demonstrates the preliminary simulation of the idea to develop an FPGA based digital circular polarizer. It describes the digital signal processing in FPGA and the experimental verification of the technique to show that good polarization purity is obtained. It also describes the significance and application of the digital circular polarizer in VLBI in radio astronomy and finally visits the remaining topics to be discussed..

# **CHAPTER 2**

## THEORETICAL DEVELOPMENT

In this chapter I first provide an introductory paragraph on the significance of theoretical analysis. Then I provide an overview of the method to convert from linear to circular polarization. Next I describe phase and gain equalization after which I provide details on windowing of the resulting phase and gain equalization parameters. Then I describe the method to form circular polarization. Next is performance limitations due to D-term and temporal instability of receivers and subsequently I provide details on the stability of analogue receiver chains in Effelsberg telescope. Next I estimate the resulting polarization purity considering the sensitivity of polarization leakage to phase errors as obtained under performance limitation due to D-terms and existing phase errors in analogue receiver chains in Effelsberg. Finally I provide introductory text on the next chapter.

# 2.1 Significance of theoretical analysis

After exploring the preliminary idea to form circular polarization digitally, I proceeded to prove that this could be implemented in practice. Hence, it was needed to verify theoretically that the idea is sound so that no question is raised on its validity. All the formulations done by me unless specified are shown in order to manifest the understandability and to negate any ambiguity against the idea. The digital signal processing shown here encompasses the basis for FPGA implementation confirming that FPGA implementation could begin unquestionably. We have also taken into account the performance limitations due to D-terms and variability of analogue receiver transfer characteristics. Taking all the factors into account we came to the conclusion that excellent polarization purity can be achieved by this method. The channel width and the number of channels are variable and can be adapted to one's need. We decided to keep the numbers optimum covering 200 % fractional bandwidth (500 MHz) and keeping 1 MHz channel width so that the implementation can be done in reasonable number of FPGA chips and simultaneously achieving the goal to obtain better polarization purity than the analogue circular polarizers over broad bands.

# 2.2 Method overview

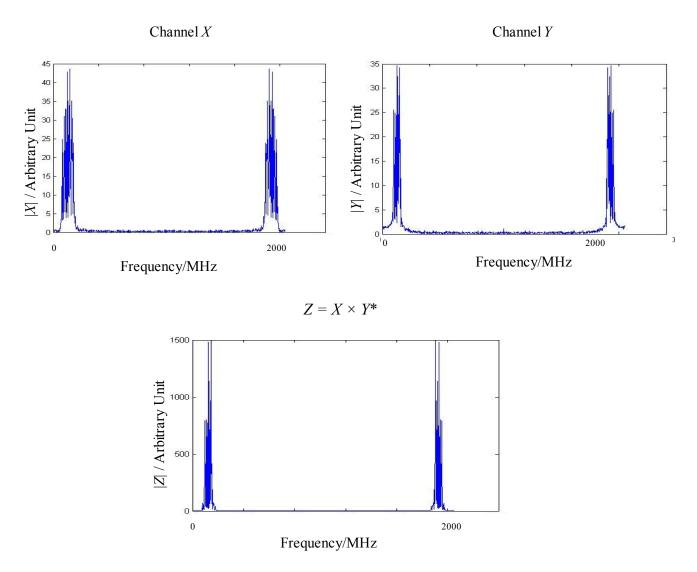

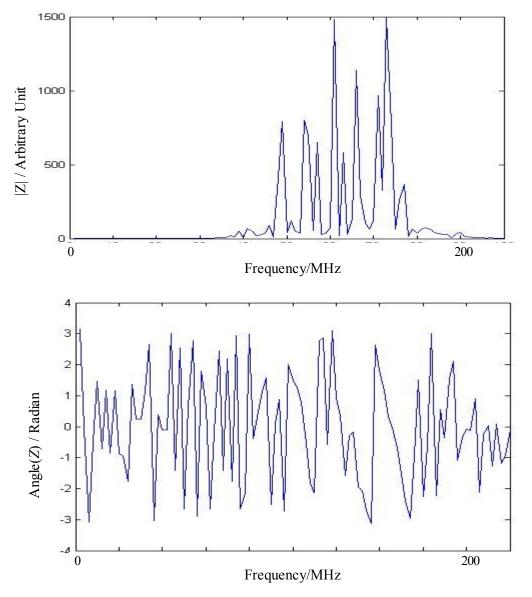

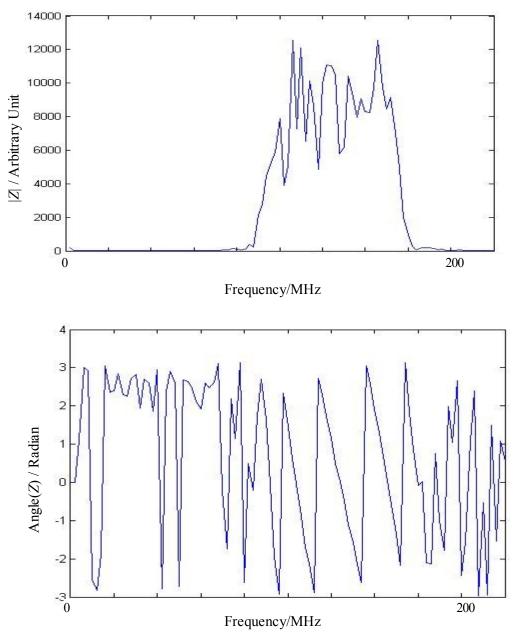

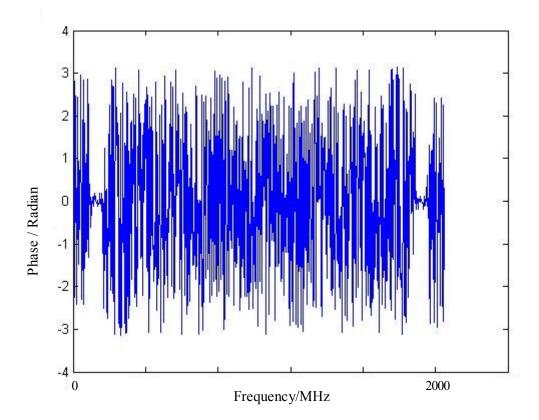

The noise diode signals during calibration pass through the same x and y receiving chains as does the astronomical signal later, and are sampled at IF at 1 GSamples/s (i.e. 500 MHz contiguous Nyquist bandwidth). The sampled x(t) and y(t) signals are processed in an FX correlator on the FPGA, which transforms to frequency domain with 1 MHz channel widths, cross multiplies each  $X(\omega)$  spectrum against the corresponding  $Y(\omega)$  spectrum and integrates for 8 s. We chose a spectral resolution of 1 MHz to allow for possibly rapidly changing channel phase differences with frequency. The result is a phase spectrum with low thermal phase noise that represents the phase difference between the x and ychannels due to the transfer characteristics of the receiver chains. The phase spectrum is used during later astronomical observation for equalizing the (frequency-dependent) phase lengths of the x and yreceiver chains. The x and y bandpass amplitude shapes are also equalized, using gains derived during calibration from total-power spectra of  $X(\omega)$  and  $Y(\omega)$  accumulated during the calibration stage. To form circular polarization from native linears during astronomical observations, we need likewise to transform the x(t) and y(t) time series to frequency domain in the same manner as during calibration, then equalize the transfer characteristics by applying a phase rotation to each frequency channel of one polarization and an amplitude scaling to each frequency channel of both polarizations in an equalizer stage, then simply add or subtract 90° (equivalent to exchanging real and imaginary in the complex spectra), and summing to form results that respond to the two hands of circular polarization.

#### 2.3 Instrumental phase and gain calibration

The orthogonal time-domain field components x(t) and y(t) received by the crossed dipoles undergo unequal phase and amplitude distortions due to different frequency-dependent time delays and gains of the two receiving systems through which they pass. The phase and gain calibration aims to compensate the transfer characteristics of channel x and channel y to make them identical in x(t) and y(t), reducing instrumental artifacts to zero. This approach is already used in software for calibrating radio astronomical data though those operate on stored data rather than in real time. Our effort is to extend it to the digital domain processing sampled IF signals in real time, calibrating with fine frequency channels, to enable formation of circular polarization in real time with more accurate phase and magnitude response than the analogue techniques can achieve over broad bandwidths. I have not considered channel non-linearities and multi-path effects. Non-linearity spreads the output spectrum beyond the input spectrum by introducing new frequency components and causes amplitude distortion. Therefore, radio astronomical receivers have to be designed to be linear. In the presence of strong RFI (radio frequency interference) non-linearity does occur and has to be blanked. Techniques for RFI mitigation are a sizable study in themselves and are beyond the scope of the present work. Nevertheless RFI mitigation techniques can easily be implemented in the same digital hardware. For the present development I assume linear transfer characteristics and Gaussian signal statistics. We have filtered the passband to avoid aliasing and kept signal levels in the linear regime. A linear time invariant system causes only pulse dispersion and amplitude scaling.

# 2.3.1 Phase equalization

Let us consider the noise diode signal during calibration as a broadband source radiating Gaussian random signals continuously in time, s(t), and I receive and sample a finite number,  $N_s$ , of frames of time-domain samples each consisting of N samples spaced equally in time in two orthogonal linear polarization states, x(t) and y(t). Let the sampled time series be represented by  $x_i(t)$  and  $y_i(t)$  and the noise diode signal at the sample times be  $s_i(t)$  where  $i = 1, 2, 3, ..., N_s$ . It is convenient to transform these time series into the frequency domain since the transfer characteristic of the receiving system used for calibration is frequency dependent. The Fourier transform produces  $N_s$  spectra, each consisting of N channels.  $N_s$  depends on the sampling rate,  $f_s$ , the number of samples in a spectrum, N, and the total integration time,  $T_{integ}$ , as

$$N_s = (f_s \times T_{integ})/N \tag{2.1}$$

Let a time-domain signal have length  $T_0$ , then the corresponding frequency-domain spectrum will have channels spaced at an interval  $f_0$  of  $1/T_0$  frequency units. For a simplified analysis I consider one frequency component, the results from which hold good for all other spectral components in the band.

The signals  $x_i(t)$  and  $y_i(t)$  are represented by the equations

$$x_{i}(t) = h_{x}(t) * (s_{i}(t) + n_{xi}(t)) , \qquad (2.2)$$

$$y_{i}(t) = h_{y}(t) * (s_{i}(t - t_{xy}) + n_{yi}(t))$$

(2.3)

where  $h_x(t)$  and  $h_y(t)$  are the transfer functions of channel x and channel y,  $t_{xy}$  is the x-y

propagation time difference from the dipoles to the receiver inputs (samplers for a digital receiver), and  $n_{xi}(t)$  and  $n_{yi}(t)$  are external unwanted signals (astronomical sources, thermal fluctuations and spurious sources). After transforming to the frequency domain these relations are

$$X_{i}(\boldsymbol{\omega}) = |X_{i}(\boldsymbol{\omega})| e^{j \Phi_{x}(\boldsymbol{\omega})}$$

(2.4)

$$= |H_X(\omega)| e^{j\theta_X(\omega)} [S_i(\omega) + N_{Xi}(\omega)] , \text{ and}$$

(2.5)

$$Y_i(\boldsymbol{\omega}) = |Y_i(\boldsymbol{\omega})| e^{j \phi_r(\boldsymbol{\omega})}$$

(2.6)

$$= |H_{Y}(\boldsymbol{\omega})|e^{j\theta_{Y}(\boldsymbol{\omega})}(S_{i}(\boldsymbol{\omega})e^{-j\omega t_{y}} + N_{Yi}(\boldsymbol{\omega}))$$

(2.7)

where  $\Phi_X(\omega)$  and  $\Phi_Y(\omega)$  are the phases of  $X_i(\omega)$  and  $Y_i(\omega)$  respectively and  $\Theta_X(\omega)$  and  $\Theta_Y(\omega)$  are the phases of the transfer functions  $H_X(\omega)$  and  $H_Y(\omega)$  respectively. The phase difference  $\Phi_X(\omega)$  -  $\Phi_Y(\omega)$  is due to the initial and instrumental phase difference between  $X(\omega)$  and  $Y(\omega)$ .

Now, let us consider the samples of  $X_i(\omega)$  and  $Y_i(\omega)$  at uniform intervals of  $\omega_0 = 2\pi f_0$ . If  $X_i(r\omega_0)$  and  $Y_i(r\omega_0)$  are the  $r^{th}$  (channel number) samples of  $X_i(\omega)$  and  $Y_i(\omega)$  respectively, where  $r = 0, 1, 2, 3, \dots, N$ -1, then equations 2.4, 2.5, 2.6 and 2.7 can be rewritten in discrete form (Cooley & Tukey 1965) as

$$X_i(\mathbf{r}\,\mathbf{\omega}_0) = |X_i(\mathbf{r}\,\mathbf{\omega}_0)| e^{j\,\Phi_x(\mathbf{r}\,\mathbf{\omega}_0)}$$

(2.8)

$$= |H_X(r\boldsymbol{\omega}_0)| e^{j\boldsymbol{\theta}_X(r\boldsymbol{\omega}_0)} (S_i(r\boldsymbol{\omega}_0) + N_{Xi}(r\boldsymbol{\omega}_0))$$

(2.9)

$$Y_i(r\,\boldsymbol{\omega}_0) = |Y_i(r\,\boldsymbol{\omega}_0)| \, e^{j\,\boldsymbol{\Phi}_r(r\,\boldsymbol{\omega}_0)} \tag{2.10}$$

$$= |H_{Y}(r\omega_{0})|e^{j\theta_{Y}(r\omega_{0})}(S_{i}(r\omega_{0})e^{-jr\omega_{0}K_{1}T_{s}} + N_{Yi}(r\omega_{0}))$$

(2.11)

where  $K_1$  is the fractional sample delay caused by  $t_{xy}$  and  $T_s$  is the sampling period. It is assumed that the system is linear. Thus the transfer function causes only linear distortion and no new frequency components are produced. The resulting pulse is dispersed in time and amplitude rescaled. The phase difference  $\Phi_X(r\omega_0) - \Phi_Y(r\omega_0)$  is obtained from the accumulated cross power spectrum of  $X_i(r\omega_0)$  and  $Y_i(r\omega_0)$  in the frequency domain, which is expressed as

$$Z(r\,\omega_{0}) = \sum_{i=1}^{N_{s}} Z_{i}(r\,\omega_{0})$$

(2.12)

$$= \sum_{i=1}^{N_s} |X_i(r \,\omega_0)| |Y_i(r \,\omega_0)| e^{j(\phi_x(r \,\omega_0) - \phi_y(r \,\omega_0))}.$$

(2.13)

Using Eq.(2.9) and Eq.(2.11) in Eq.(2.13) I obtain the product  $|X_i(r\omega_0)||Y_i(r\omega_0)|e^{j(\phi_x(r\omega_0)-\phi_y(r\omega_0))}$ , which consists of the summation of the following contributing terms

1.

$$|H(r \omega_0)| e^{j \theta(r \omega_0)} |S_i(r \omega_0)|^2 e^{j r \omega_0 K_1 T_s}$$

(2.14)

2.

$$|H(r \omega_0)|e^{j\theta(r \omega_0)}N'_{Y_i}(r \omega_0)N_{X_i}(r \omega_0)$$

(2.15)

where

$$|H(r\omega_0)|e^{j\theta(r\omega_0)} = |H_X(r\omega_0)||H_Y(r\omega_0)|e^{j(\theta_X(r\omega_0)-\theta_Y(r\omega_0))}$$

$Z_i(r\omega_0)$  is accumulated for  $T_{integ}$  time. Since  $S_i$  is incoherent with  $N_{Xi}$  and  $N_{Yi}$ , their cross product terms will average to zero in the summation and so are not shown here. We have chosen, in practice, 8 s integration time corresponding to  $8 \times 10^6$  frames of data so that the thermal fluctuations of the noise diode signal that is 5 % of the system temperature are averaged down to a fractional fluctuation of  $4 \times 10^{-4}$  in 1 MHz channels. Thus we attain our objective of measuring the transfer characteristic phase to 0.1° precision. At such high levels of precision, the measurement is sensitive to corruption by possible external sources or by RFI via the second term Eq. (2.15). I cancel this effect on our measurement of the transfer characteristic, provided the corrupting source remains constant, by performing the summation in Eq. (2.13) twice, first in the presence of  $s_i(t)$  (noise diode switched on) and second with  $s_i(t)=0$  (noise diode switched off) and differencing. Hence, considering only the first term (Eq. 2.14) I obtain the phase difference  $\Phi$  between the two polarization signals due to instrumental effects and due to any initial phase difference as follows

$$\Phi = \Phi_{instrument} + \Phi_{initial} \tag{2.16}$$

where,  $\phi_{instrument} = \theta(r\omega_0)$  and  $\phi_{initial} = r\omega_0 K_1 T_s$ . I have not considered any frequency down conversion in Eqs. (2.9) and (2.11). A down conversion will cause a frequency shift in  $\omega$  by an amount  $\omega_d$  where  $\omega_d$  is the mixing frequency. Then the samples of  $\omega$  in Eqs. (2.9) and (2.11) or  $r\omega_0$  will represent the samples of  $\omega - \omega_d$ . The equations will remain unchanged except for the initial phase, which will now be  $(r\omega_0 + \omega_d)K_1T_s$  so that the initial phase is unaffected by down conversion.

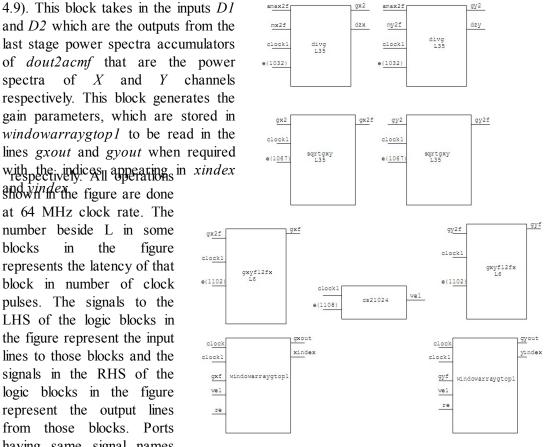

For accurate calibration,  $\Phi_{instrument}$  should be measured and used later to correct the signals for the effect of  $\phi_{instrument}$ . This should reduce the phase difference to zero, requiring that the initial phase difference be zero so that  $\phi$  corresponds to instrumental phase errors only. This requires that the two orthogonal dipoles receive signal from a common source placed at a location equidistant from both the dipoles, which is accomplished by placing a noise source at 45° to the two dipoles. One could alternatively calibrate using a polarized astronomical source instead of the noise diode, and point on source and then off source for the two accumulations to be differenced. In the on-source position, the dish main beam must be pointed accurately to the source, placing the source on the focal axis. The dipoles are located in a plane accurately perpendicular to the focal axis and hence, the dipoles would be equidistant from the source to high accuracy, so  $\phi_{initial}$  would be close to zero and can be ignored.  $Z(r\omega_0)$  gives the angle through which one of the vectors say  $Y(r\omega_0)$  must be rotated to make the phase lengths of the two polarization channels equal. The frequency-dependent rotation matrix elements  $\cos\theta(r\omega_0)$  and  $\sin\theta(r\omega_0)$  are obtained without trigonometric functions for computational efficiency using the relations

$$\cos\theta(r\,\omega_0) = \Re\left(Z(r\,\omega_0)\right) / |Z(r\,\omega_0)| \quad , \tag{2.17}$$

$$\sin \Theta(r \,\omega_0) = \Im \left( Z(r \,\omega_0) \right) / \left| Z(r \,\omega_0) \right| \tag{2.18}$$

Let  $Y'(r\omega_0)$  be the vector obtained after rotation of vector  $Y(r\omega_0)$  by the phase difference

$\Theta(r\omega_0)$  . Then the phase difference between  $X(r\omega_0)$  and  $Y'(r\omega_0)$  reduces to zero or

$$\boldsymbol{\Phi}_{X}(\boldsymbol{r}\,\boldsymbol{\omega}_{0}) - \boldsymbol{\Phi}_{Y}(\boldsymbol{r}\,\boldsymbol{\omega}_{0}) = 0 \tag{2.19}$$

as required for a correctly calibrated system phase prior to formation of circular polarization.

#### 2.3.2 Gain equalization

The amplitudes also undergo linear distortions due to different gains in the two channels due to different passband characteristics. To compensate the amplitude differences, all the spectral components of  $X_i(\omega)$  and  $Y_i(\omega)$  in the passband are scaled to one same level, chosen to be the maximum signal level,  $V_{max}$  in the passbands of  $X_i(\omega)$  and  $Y_i(\omega)$ . Multiplying Eq. (2.5) with its complex conjugate, I obtain the power spectrum  $|X_i(\omega)|^2$  and similarly Eq. (2.7) yields  $|Y_i(\omega)|^2$ . The scaling factors to equalize the magnitudes of  $X_i(r\omega_0)$  and  $Y_i(r\omega_0)$  are obtained from accumulating  $|X_i(r\omega_0)|^2$  and  $|Y_i(r\omega_0)|^2$  respectively for  $T_{integ}$  to reduce thermal noise fluctuations in the measurement of the passband shapes and are expressed by the following two equations:

$$|X(r\omega_0)|^2 = \sum_{i=1}^{N_s} |X_i(r\omega_0)|^2$$

(2.20)

$$|Y(r\omega_0)|^2 = \sum_{i=1}^{N_s} |Y_i(r\omega_0)|^2.$$

(2.21)

Expanding these using Eqs. (2.9) and (2.11) I find that each contains the following contributing terms for summation:

1.

$$|H_X(r \omega_0)|^2 |S_i(r \omega_0)|^2$$

, (2.22)

$$|H_{Y}(r \omega_{0})|^{2} |S_{i}(r \omega_{0})|^{2} , \qquad (2.23)$$

2.

$$|H_{X}(r \omega_{0})|^{2} |N_{Xi}(r \omega_{0})|^{2}$$

, (2.24)

$$|H_{Y}(r\omega_{0})|^{2}|N_{Yi}(r\omega_{0})|^{2}$$

(2.25)

where  $\Phi_{N_{xi}}(r\omega_0)$  and  $\Phi_{N_{yi}}(r\omega_0)$  are the phases of  $N_{xi}(r\omega_0)$  and  $N_{yi}(r\omega_0)$  respectively.

The first term (Eqs. 2.22 and 2.23) provides the measurement of the bandpass shape that I seek (assuming that the noise diode produces white noise). The second term (Eqs. 2.24 and 2.25) does not average to zero to the extent that noise sources other than the noise diode (eg receiver noise, radio sources, atmospheric emission, cosmic microwave background, and RFI) are present. I cancel this term, provided the corrupting source remains constant, by performing the summation in Eqs. (2.20) and (2.21) twice, first in the presence of  $s_i(t)$  (noise diode switched on) and second with  $s_i(t)=0$  (noise diode switched off) and differencing. Hence, I am left with only the first term (Eqs. 2.22 and 2.23) where  $|H_x(r\omega_0)|^2$  and  $|H_y(r\omega_0)|^2$  are the frequency-dependent amplitude scaling factors. To determine the gains  $g_x(r\omega_0)$  and  $g_y(r\omega_0)$  that scale each  $X_i(r\omega_0)$  and  $Y_i(r\omega_0)$  to equalize the passband amplitudes to the same level, the following two equations are used

$$g_X(r\,\omega_0) = \sqrt{P_{max}/|X(r\,\omega_0)|^2} \quad , \tag{2.26}$$

$$g_{Y}(r\boldsymbol{\omega}_{0}) = \sqrt{P_{max}/|Y(r\boldsymbol{\omega}_{0})|^{2}} \quad .$$

(2.27)

$P_{max}$  in Eqs. (2.26) and (2.27) is obtained by comparing all  $|X(r\omega_0)|^2$  and  $|Y(r\omega_0)|^2$  of Eqs. (2.20) and (2.21) for  $r = 0, 1, 2, 3, \dots, N-1$  and finding the maximum power. The gains in Eqs. (2.26) and (2.27) are calculated using accumulated power spectra and are later applied to voltage spectra for equalization, which potentially introduces a small inaccuracy since the gains thus obtained are not the same as the actual gains obtained by accumulating individual voltage spectra consisting of absolute voltages in the denominators. However, if the absolute voltages,  $|X_j(r\omega_0)|$  and  $|Y_j(r\omega_0)|$ , where  $j=N_s+1, N_s+2, \dots$  for the subsequent spectra acquired during observations, are accumulated for sufficient integration time then

$$g_X(r\omega_0) \approx V_{max} / \sum |X_j(r\omega_0)|$$

, and (2.28)

$$g_{Y}(r\omega_{0}) \approx V_{max} / \sum |Y_{j}(r\omega_{0})| \quad .$$

(2.29)

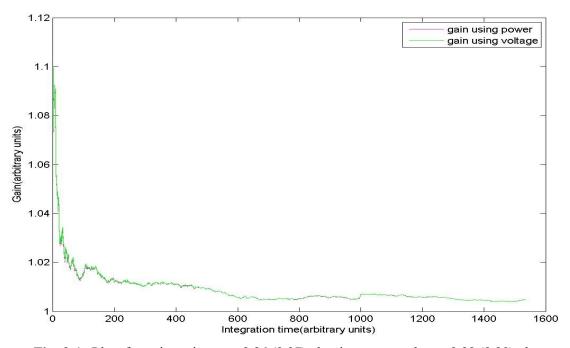

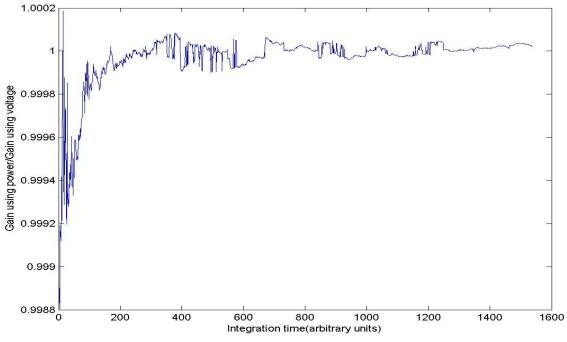

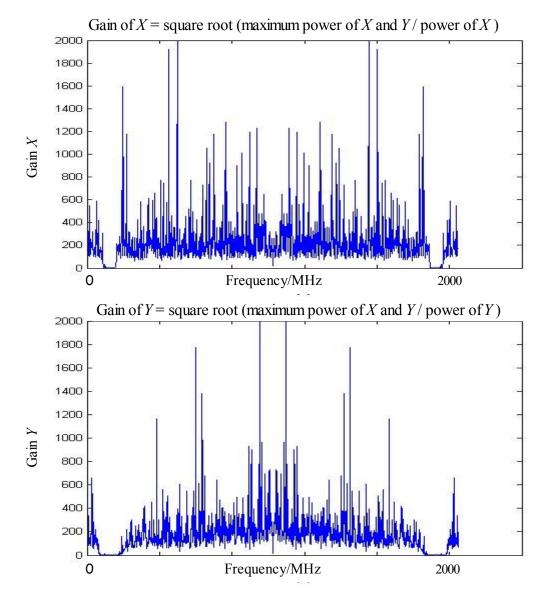

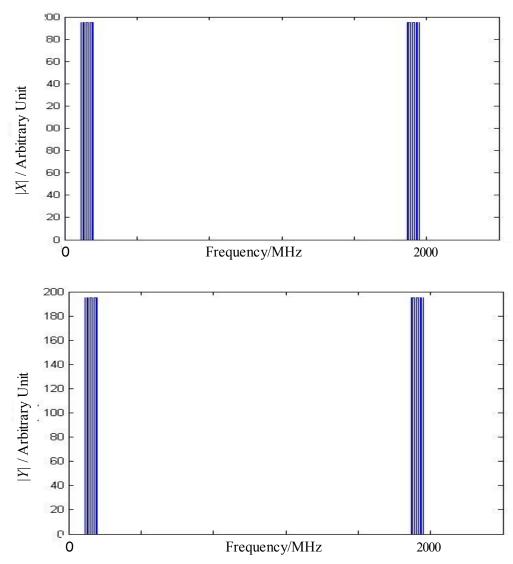

$V_{max}$  in Eqs. (2.28) and (2.29) is the maximum of all  $\sum |X_j(r\omega_0)|$  and  $\sum |Y_j(r\omega_0)|$  for  $r = 0, 1, 2, 3, \dots, N-1$ . Eqs. (2.28) and (2.29) are also confirmed in numerical simulation. Fig. 2.1 as shown below illustrates this.

**Fig. 2.1:** Plots for gains using eqn. 2.26 (2.27), that is, power and eqn. 2.28 (2.29), that is, voltage for a single channel of one polarization as a function of integration time. Both are approximately same.

I have just plotted the gains for the first channel. But all of them show similar effects. The ratio of gain

derived using power and gain derived using voltage is shown in fig. 2.2. The ratio approaches unity as the number of samples included in the summation increases or integration time increases.

**Fig. 2.2:** Ratio of gains obtained by using eqn. 2.26 (power) and eqn. 2.28 (voltage). It approaches unity with increase in integration time.

The plots in figures 2.1 and 2.2 are generated in the following steps.

1) I generated a matrix of random numbers of dimension  $N \times 1024$  and augmented all the elements by 5 to enhance the visibility of the plots. The number 1024 represents number of channels and N is the upper limit of the count up to which each channel's element can be incremented. N is taken as 1550. Another variable i takes the values from 5 to N, which means that at least 5 numbers pertaining to a particular channel should be added and then this number would increase up to N.

2) Formula 2.26 (2.27) is compared against 2.28 (2.29) for consecutively increasing integration time or count i and the result is shown in fig. 2.1. The two overlapping curves verify that 2.26 (2.27) and 2.28 (2.29) produces approximately the same results. The plot is for a single channel.

3) Fig. 2.2 shows the plot for  $2.26 \div 2.28$  (same for  $2.27 \div 2.29$ ) demonstrating that the two equations 2.26 and 2.28 (2.27 and 2.29) produce more and more identical results as the count is increased or their ratio tends towards unity.

# 2.4 Windowing

A window function is derived for the  $X_j$  and  $Y_j$  spectra to truncate the possible analogue filter flanks to avoid scaling up, by large factors, signals that have been strongly attenuated by band-limiting filters. The window function is conveniently obtained from the |Z| spectrum since the Z spectrum contains the band common to both X and Y spectra thereby providing necessary frequency shift and bandwidth information for the window function. Spectral channels in which the signal level  $|Z(r\omega_0)|$  is greater than one quarter of the maximum amplitude in the |Z| spectrum are given unit

16

weight and all others are given zero weight resulting in a frequency shifted rectangular function of unit amplitude. A unit delta function is added to this since we want to pass undisturbed the DC signal produced by the A/D converter. This window function is applied to both  $X_j$  and  $Y_j$  spectra resulting in rectangular band shape for the frequency band that is in common. The effect of the window function on the time-domain is to convolve the signal with a sinc function. Since, the frequency spectra are already band limited, the window function does not in itself introduce any new waveform characteristics. Rather it prevents contamination of the waveform that would arise were one to scale up, by large factors, frequency channels that had little signal.

# 2.5 Forming circular polarization

The gains  $g_X(r\omega_0)$  and  $g_Y(r\omega_0)$ , the rotation parameters  $\sin\theta(r\omega_0)$  and  $\cos\theta(r\omega_0)$ , and the window function  $W(r\omega_0)$  are applied to the spectral components  $X_j(r\omega_0)$  and  $Y_j(r\omega_0)$  respectively. If  $Y'_j(r\omega_0)$  and  $X'_j(r\omega_0)$  are the resulting vectors after calibration then  $Y'_j(r\omega_0)$  is related to  $Y_j(r\omega_0)$  by the product of gain, window function and rotation matrix as follows

$$\begin{vmatrix} \Re (Y_j''(r\omega_0)) \\ \Im (Y_j''(r\omega_0)) \end{vmatrix} = g_Y(r\omega_0) W(r\omega_0) \begin{vmatrix} \cos \theta(r\omega_0) & -\sin \theta(r\omega_0) \\ \sin \theta(R\omega_0) & \cos \theta(r\omega_0) \end{vmatrix} \times \begin{vmatrix} \Re (Y_j(r\omega_0)) \\ \Im (Y_j(r\omega_0)) \end{vmatrix}$$

(2.30)

where  $\Re(Y_j''(r\omega_0))$ ,  $\Im(Y_j''(r\omega_0))$  and  $\Re(Y_j(r\omega_0))$ ,  $\Im(Y_j(r\omega_0))$  are real and imaginary components of  $Y_j''(r\omega_0)$  and  $Y_j(r\omega_0)$  respectively. Similarly,

$$\begin{aligned} & \left| \Re \left( X_{j}'(r \, \boldsymbol{\omega}_{0}) \right) \\ \Im \left( X_{j}'(r \, \boldsymbol{\omega}_{0}) \right) \end{aligned} = g_{X}(r \, \boldsymbol{\omega}_{0}) W(r \, \boldsymbol{\omega}_{0}) \left| \Re \left( X_{j}(r \, \boldsymbol{\omega}_{0}) \right) \\ \Im \left( X_{j}(r \, \boldsymbol{\omega}_{0}) \right) \end{aligned}$$

(2.31)

The windowed, phase and gain calibrated  $X'_{j}(r\omega_{0})$  and  $Y''_{j}(r\omega_{0})$  are added in quadrature (± 90°) to obtain RHC and LHC polarizations.

# **2.6 Performance limitations**

In this section we will discuss the implications of possible contamination of phase caused by the cross polar component or leakage of unwanted orthogonal polarization component (D-terms) and by the temporal instability of receiver transfer characteristics and their effects on polarization purity with approximate quantitative results to estimate those errors. we will also discuss the requirement of frequent recalibration due to the variations in the transfer characteristics of the receiver by observing the drifts in the most sensitive parameters, which are the channel phases. Since the gain fluctuations are much smaller than phase fluctuations, we can ignore their effects.

Effect of phase error on polarization purity:

Were one to introduce an imperfect 90° phase shift into one channel when forming circular polarization from perfectly orthogonal linearly polarized channels, the output voltages  $\bar{V}_{RHC}$  and  $\bar{V}_{LHC}$  would contain unwanted contributions from the opposite hand of polarization. The derivation below was originally given to me by Alan Roy and I did some modifications and we arrived at the following

derivation together.

$$\bar{V}_{LHC} = V_{LHC} + \left( D_{LHC} V_{RHC} \right) \tag{2.32}$$

$$\bar{V}_{RHC} = V_{RHC} + (D_{RHC} V_{LHC})$$

(2.33)

where  $D_{LHC}$  and  $D_{RHC}$  are the fractional voltage leakage factors from unwanted polarizations (D-terms).

The larger the phase error, the greater the contribution from the opposite hand. Consider the monochromatic case in which a linearly polarized wave is incident normally on crossed linear dipoles with the plane of the electric field oriented at 45° to the two dipoles. Then the voltages in the two dipoles are

$$V_x = V_0 e^{j\omega t} \tag{2.34}$$

$$V_{v} = V_{0} e^{j\omega t} \tag{2.35}$$

After introducing an imperfect 90° phase shift to the y channel, one has

$$V_x = V_0 e^{j\omega t} \tag{2.36}$$

$$\overline{V}_{v} = \pm j V_{0} e^{j\omega t} e^{j\epsilon}$$

(2.37)

where  $\epsilon$  is the error in the 90° phase shift. Circular polarization is obtained by summing the x signal with the imperfectly phase-shifted y signal, giving

$$\bar{V}_{LHC} = V_0 e^{j\omega t} (1 - j e^{j\epsilon})$$

(2.38)

$$\bar{V}_{RHC} = V_0 e^{j\omega t} \left(1 + j e^{j\epsilon}\right) \tag{2.39}$$

Had the 90° phase shift been perfect, then  $\epsilon = 0^{\circ}$  giving  $\bar{V}_{LHC} = V_{LHC}$  and  $\bar{V}_{RHC} = V_{RHC}$ . Substituting Eq.(2.38) and Eq.(2.39) into Eqs.(2.32) and (2.33) respectively, with  $V_{LHC}$  and  $V_{RHC}$  obtained by setting  $\epsilon = 0$ , we obtain the dependence of  $D_{LHC}$  and  $D_{RHC}$  on the phase error,  $\epsilon$ :

$$D_{LHC} = -D_{RHC} = [1 + \sin \epsilon - \cos \epsilon + j(1 - \sin \epsilon - \cos \epsilon)]/2$$

(2.40)

This result is used in section 2.8 for estimating the polarization purity.

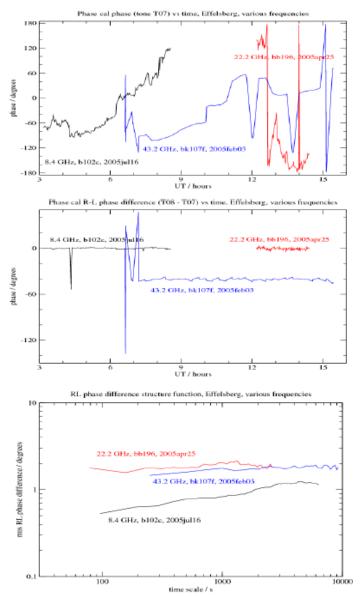

#### 2.7 Phase stability of the analogue receiver chain

This section and the following section taken from our paper (Das et. al. 2010) is contributed by Alan Roy. The phase and amplitude transfer characteristics of the receiver chains for the orthogonal polarization channels are known to drift with time, due primarily to temperature changes of filters and cables used in the receiver chains. Fortunately, most of that change is common to both orthogonal polarization channels as the equipment for both channels is housed in close proximity to each other, and the relative changes are small compared to the total. The effect of drift in the relative transfer

characteristic is a degradation of the polarization purity, since the equalizer weights that were determined prior to an observation would no longer perfectly correct the channel differences, by the amount of the relative drift since that determination was made. This translates into a requirement that the equalizer weights be re-determined periodically to ensure that polarization impurity due to drift remains below a pre- determined level. We have estimated how often such re-determination would need to be made by measuring the relative phase drift in some existing receiver chains at Effelsberg and the VLBA. The measurements were made using the VLBI phase calibration system (Thompson 1991), which injects a pulse train in the front end and extracts them at the backend data acquisition rack or correlator, to monitor the phase length of the whole receiver system, from front end to the samplers. The measurements show that indeed the phase changes in the orthogonally-polarized channels track each other well (Fig 2.3 top and middle) and there are only occasional outliers, most likely related to

**Fig. 2.3:** Top: calibration system phase vs time for a single polarization channel for three different receivers at Effelsberg, showing phase changes of typically to over periods of hours. Middle: calibration system phase difference between orthogonal polarizations of the same receivers at Effelsberg, for the identical experiments as in the top plot with an arbitrary offset. Bottom: structure functions constructed from the relative phases presented in the middle plot. These show the rms of the phase difference vs time-scale.

# 2.8 Expected polarization purity

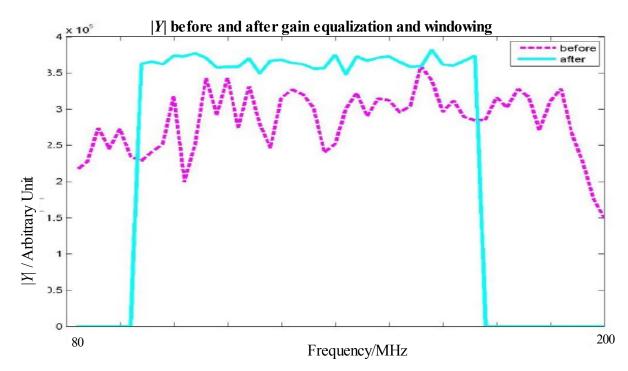

The polarization purity to be expected from polarization conversion performed at IF can be derived by combining the two results from section 2.6 and 2.7 - the sensitivity of polarization leakage to phase errors and the typical phase errors in existing analogue receiver chains ( $0.5^{\circ}$  to  $2^{\circ}$  rms).