## Exact Integer Programming Approaches to Sequential Instruction Scheduling and Offset Assignment

Inaugural-Dissertation

zur

Erlangung des Doktorgrades

der Mathematisch-Naturwissenschaftlichen Fakultät

der Universität zu Köln

vorgelegt von Sven Mallach aus Duisburg

Köln2015

Berichterstatter:Prof. Dr. Michael Jünger(Gutachter)Prof. Dr. Peter Marwedel

Tag der mündlichen Prüfung: 15.01.2015

# Zusammenfassung

Die vorliegende Dissertation berichtet über die wesentlichen Konzepte und Resultate wissenschaftlicher Studien zur exakten Lösung zweier  $\mathcal{NP}$ -schwerer Compiler-Optimierungsprobleme, *Instruction Scheduling* und *Offset Assignment*, mittels ganzzahliger linearer Programmierung. Sie ist das Ergebnis mehrjähriger Forschung als wissenschaftlicher Mitarbeiter am Lehrstuhl von Michael Jünger in Köln, mit einer besonderen Ausrichtung darauf, mathematische Optimierungsverfahren auf praktische Problemstellungen aus dem Bereich der technischen Informatik anzuwenden.

Die beiden behandelten Probleme sind im Wesentlichen völlig unabhängig voneinander, beschäftigen sich aber beide mit der Zuteilung von beschränkt zur Verfügung stehenden Ressourcen und treten während der Erzeugung von Maschinencode innerhalb eines Compilers auf. Instruction Scheduling behandelt die Zuteilung von Taktzyklen zu Instruktionen mit dem Ziel, die Gesamtausführungszeit aller Instruktionen zu minimieren. Diese Zuteilung muss Datenabhängigkeiten, Latenzbedingungen und Ressourcenbeschränkungen berücksichtigen. Beim Offset Assignment geht es um Speicherlayouts von Programmvariablen und den effizienten Einsatz von Adressregistern für Zugriffe auf diese Variablen, so dass der erforderliche Zusatzaufwand in Form von expliziten Adressberechnungen minimiert wird. Im Gegensatz zum Instruction Scheduling, das Bestandteil nahezu jedes Compilers ist, tritt das Offset Assignment Problem hauptsächlich bei Compilern für spezialisierte Prozessorarchitekturen auf.

Instruction Scheduling ist ein bereits sehr intensiv studiertes Problem, zu dem diverse exakte und heuristische Verfahren entworfen und experimentell analysiert wurden. Diese Arbeit konzentriert sich auf das Basic-Block Instruction Scheduling Problem für Single-Issue Prozessoren. Basic Blocks sind Programmfragmente mit einem einzigen Einstiegs- und Ausstiegspunkt. Es müssen daher alle Instruktionen eines Basic Blocks ausgeführt werden, bevor der Kontrollfluss zu einem anderen Basic Block übergeht. Single-Issue Prozessoren sind in der Lage, pro Taktzyklus mit der Ausführung exakt einer neuen Instruktion zu beginnen. Eine Reihe von Techniken zur Vorbehandlung von Basic Block Instanzen wurden in der Literatur vorgestellt. Sie werden, mit einem Schwerpunkt auf aktuellere Verfahren seit dem Jahr 2000, in dieser Arbeit ausgiebig diskutiert, denn sie führten zu einem Constraint Programming Ansatz im Jahr 2006, der etwa 350000 Instanzen optimal lösen konnte, wobei einige dieser Instanzen bis zu 2500 Instruktionen beinhalten. Der letzte Versuch, das Problem mittels ganzzahliger Programmierung zu lösen, datiert hingegen aus einer Zeit vor Veröffentlichung der jüngsten Vorbehandlungsmethoden. Es erwies sich bei sehr restriktiven Latenzbedingungen als erfolgreich, konnte aber hunderte der soeben benannten Instanzen, die große und stärker variierende Latenzen beinhalten, nicht lösen. Des Weiteren basieren nahezu alle bisher vorgestellten Verfahren auf sogenannten zeitindizierten Formulierungen, bei denen Entscheidungsvariablen eine explizite Zuweisung von Instruktionen zu Taktzyklen modellieren. Die vorliegende Arbeit beschreibt hingegen einen vollkommen neuen Ansatz basierend auf dem Linearen Ordnungsproblem, das ein bereits sehr gut studiertes kombinatorisches Optimierungsproblem ist. Die neuen Modelle führen zu einer alternativen Charakterisierung der zulässigen Lösungen des Basic-Block Instruction Scheduling Problems. Sie ermöglichen den Einsatz von Branch-and-Cut Algorithmen, die auch größere Instanzen lösen können. Die Formulierungen werden außerdem durch zusätzliche Ungleichungen erweitert, die als Schnittebenen verwendet werden können. Kombiniert mit den Methoden zur Vorbehandlung, die zum Teil ebenfalls noch erweitert und verbessert werden, kann die entwickelte Implementierung vergleichbare Ergebnisse wie der Constraint Programming Ansatz erzielen. Dieses Ziel zu erreichen hat einige Jahre in Anspruch genommen. Die vorliegende Arbeit berichtet daher nicht nur über die entwickelten Modelle, sondern auch über diverse Ideen und Nebenprodukte, die in dieser Zeit entstanden und die inspirierend sein bzw. anderen Wissenschaftlern helfen könnten, selbst wenn sie andere Lösungsverfahren einsetzen möchten.

Die Ausgangssituation bzgl. des Offset Assignment Problems war eine andere, da insbesondere exakte Verfahren vor den in dieser Arbeit vorgestellten eher rar waren. Das Offset Assignment Problem kam in den neunziger Jahren auf und wird in diversen Varianten betrachtet, die von theoretischer und praktischer Bedeutung sind. In der einfachsten Variante wird angenommen, dass ein Prozessor lediglich ein einzelnes Adressregister und sehr limitierte Möglichkeiten zur Adressierung von Programmvariablen ohne Verursachung zusätzlichen Aufwands bietet. Selbst für diese einfachste Variante, die auch als Baustein für komplexere dient, ist das Berechnen einer Optimallösung jedoch bereits  $\mathcal{NP}$ -schwer und somit wurde das Problem im Wesentlichen im Sinne einer heuristischen Lösung studiert. Die wenigen exakten Lösungsverfahren waren nicht in der Lage, mittelgroße Instanzen zu lösen, so dass die tatsächliche Güte heuristischer Lösungen für eine lange Zeit kaum bekannt war. Auch hier zeigte sich die Untersuchung der kombinatorischen Struktur der verschiedenen Problemvarianten als Schlüsselansatz, um Branch-and-Cut Verfahren entwerfen zu können, die von bekanntem Wissen über verwandte kombinatorische Optimierungsprobleme profitieren. Die Implementierung zur Lösung der einfachsten Problemvariante war dann die erste, die die große Mehrheit von etwa 3000 Instanzen eines Standard-Benchmarks optimal lösen konnte. Im Anschluss konnten zunächst, in Zusammenarbeit mit Roberto Castañeda Lozano, zusätzliche Techniken eingebunden werden, die es dem Ansatz erlaubten, auch über den Einsatz mehrerer Adressregister zu optimieren. Erfreulicherweise konnten die Verfahren dann sogar noch weiter verallgemeinert werden, um mit flexibleren Möglichkeiten zur Adressierung von Programmvariablen umgehen zu können. Auf diese Weise beantwortet die vorliegende Arbeit nicht nur die Frage, wie groß der zusätzliche Adressierungsaufwand ist, wenn Heuristiken verwendet werden, sondern liefert auch erste Resultate, die es erlauben, die Auswirkungen flexiblerer Adressierungsmöglichkeiten auf die Laufzeit und Größe realer Anwendungen zu analysieren.

# Abstract

The dissertation at hand presents the main concepts and results derived when studying the optimal solution of two  $\mathcal{NP}$ -hard compiler optimization problems, namely *instruction scheduling* and *offset assignment*, by means of integer programming. It is the outcome of several years of research as an assistant at Michael Jünger's computer science chair in Cologne, with the particular aim to apply exact mathematical optimization techniques to real-world problems arising in the domain of technical computer science.

The two problems studied are rather unrelated apart from the fact that they both take place during the machine code generation phase of a compiler and deal with the handling of limited resources. Instruction scheduling is about the assignment of issue clock cycles to instructions in the presence of precedence, latency, and resource constraints such that the total time needed to execute all the instructions is minimized. Offset assignment deals with storage layouts of program variables and the efficient use of address registers for accesses to these variables. The objective is to employ specialized instructions in order to minimize the overhead caused by address computations. While instruction scheduling needs to be carried out by almost every present compiler irrespective of the processor architecture, the offset assignment problem occurs mainly in compilers for highly specialized processor designs.

Instruction scheduling is a well-studied field where several exact and heuristic approaches have been developed and experimentally evaluated in the past. In this thesis, we concentrate on the basic-block instruction scheduling problem for singleissue processors. Basic blocks are program fragments with no side-entrances and -exits, i.e., every instruction of a basic block needs to be executed before the control flow may leave it and enter another basic block. Single-issue processors are capable of starting the execution of exactly one instruction per clock cycle. A number of techniques to preprocess instances of the basic-block instruction scheduling problem were proposed in the literature and are, with emphasis on the more recent ones that arose since the year 2000, thoroughly reviewed in this thesis. They finally led to a constraint programming approach in 2006 that was shown to solve about 350,000 instances to optimality and where some of these instances comprised up to about 2,500 instructions. The last attempt to tackle the problem using integer programming however dates to a time prior to the publication of the latest preprocessing advances. While being successful on a set of instances that impose very restrictive latency constraints, it was shown to be unable to solve hundreds of instances from the aforementioned benchmark set that comprises also large and varying latencies.

In addition, the previous integer programming models were almost all based on socalled time-indexed formulations where decision variables model an explicit assignment of instructions to clock cycles. In this thesis, a completely different and novel approach is taken based on the *linear ordering problem*, a well-studied combinatorial optimization problem. The new models lead to alternative characterizations of the feasible solutions to the basic-block instruction scheduling problem. These facilitate the employment of advanced integer programming methodologies, in particular the design of branch-and-cut algorithms that can handle larger instances. The formulations are further extended by additional inequalities that can be used as cutting planes. Combined with the preprocessing routines that are partially extended and improved as well, the respective solver implementation eventually turned out to be competitive to the constraint programming method. Reaching this point has taken some years and this thesis presents not only the derived models but also several ideas and byproducts that arose in the meantime, and that can help and inspire researchers even if they aim at the application of different solution methodologies.

The starting point regarding the offset assignment problem was a different one because especially exact solution approaches were rather rare prior to the models presented in this thesis. The offset assignment problem arose in the 1990s and is considered in several variants that are of theoretical and practical interest. In the simplest one, a processor is assumed to provide only a single address register and only very restricted possibilities to avoid address computation overhead. However, even this simplest variant, that may serve as a building block for the more complex ones, is already  $\mathcal{NP}$ -hard and has been studied mainly from a heuristic point of view. The few existing exact solution approaches were not capable to solve moderately sized instances so that the quality of heuristic solutions relative to the optimum was hardly known at all. Again, the inspection of the combinatorial structure of the various problem variants turned out to be the key for designing branch-and-cut implementations that can profit from knowledge about related combinatorial optimization problems. The implementation targeting the simple problem variant was the first capable to optimally solve the majority of about 3,000 instances collected in a standard benchmark set. The method could then be further generalized in two steps. First, in a collaboration with Roberto Castañeda Lozano, additional techniques could be incorporated into the approach in order to handle multiple address registers. Fortunately, the methods could then even be further extended to as well deal with more flexible addressing capabilities. In this way, the thesis at hand does not only answer the question how large the address computation overhead can be when using heuristics, but as well presents first results that allow to analyze the impact of the mentioned increased addressing capabilities on the runtime performance and size of real-world programs.

# Acknowledgments

This thesis is the outcome of more than five years of research in a wonderful atmosphere thanks to some persons I cannot resist to mention at this point. First of all, I thank Michael Jünger who trusted in a young computer scientist with only a basic background in math, giving him the chance to learn about optimization. I thank you especially for the freedom to develop myself, to learn at my own speed and for giving me a warm welcome irrespective of which concern I brought into your office. I thank you for your positive attitude, for keeping superfluous load off my colleagues' and my back, for treating us as young scientists rather than as assistants.

I thank my colleagues Thomas Lange, Göntje Teuchert, Frank Baumann, Gregor Pardella, Andreas Schmutzer, Daniel Schmidt, Martin Gronemann, Christiane Spisla, Lena Tepaße, Käte Zimmer, Dustin Feld and Francesco Mambelli for fruitful discussions, nice insights, private conversations, pleasant journeys, a lot of fun, and always enough reasons to drink coffee or beer. For the same reasons, I thank Michael Belling, and of course for his support when it comes to the retrieval of hardly accessible literature. I thank Thomas and Göntje for all the administrative support that often went beyond the necessary scope. With all of you there were a lot of moments where you were more than just colleagues! I thank Roberto Castañeda Lozano for a productive collaboration, for giving me some insights into the world of constraint programming and for supporting me at my visit in Sweden. I thank Danny van Dyk for giving me a kickstart into elegant C++ when I was a computer science student. Also I thank him, Dirk Ribbrock, and Markus Geveler for being friends and for keeping up our relationships after finishing our studies. I thank Petra Mutzel and Carsten Gutwenger for their support at the very beginning of my interest and work in research. Doubtless, I thank my family and friends for their constant support during the last years. Finally, I once more thank Lena Tepaße, Roberto Castañeda Lozano, and Daniel Schmidt for their proofreading of this thesis.

# Contents

|        | Introduction                                                                                                        |              |

|--------|---------------------------------------------------------------------------------------------------------------------|--------------|

| Chapte | er 1 Preliminaries                                                                                                  | ļ            |

| 1.1.   | Combinatorial Optimization                                                                                          |              |

| 1.2.   | (Integer) Linear Programming                                                                                        |              |

| 1.3.   | Relaxations                                                                                                         |              |

| 1.4.   | Linear Programming and Polyhedral Theory                                                                            |              |

|        | 1.4.1. Combinations and Independence of Vectors, Convexity                                                          | 9            |

|        | 1.4.2. Rank and Dimension $\ldots$ | 10           |

|        | 1.4.3. Polyhedra                                                                                                    | 10           |

|        | 1.4.4. Hyperplanes, Faces and Facets                                                                                | 12           |

|        | 1.4.5. Basic Solutions and the Simplex Algorithm                                                                    | 13           |

|        | 1.4.6. Cutting Planes and their Separation                                                                          | 14           |

|        | 1.4.7. Total Unimodularity                                                                                          | 1'           |

| 1.5.   | Branch-and-Bound and Branch-and-Cut                                                                                 | 1'           |

|        | 1.5.1. Branch-and-Bound                                                                                             | 18           |

|        | 1.5.2. Branch-and-Cut                                                                                               | 19           |

| 1.6.   | Standard Linearization Approaches                                                                                   | 20           |

| 1.7.   | Constraint Programming                                                                                              | 2            |

| Chapte | er 2 Instruction Scheduling                                                                                         | 2            |

| 2.1.   | Motivation                                                                                                          | $2^{4}$      |

| 2.2.   | The Local Instruction Scheduling Problem                                                                            | $2^{\prime}$ |

|        | 2.2.1. Preparations                                                                                                 | 2            |

|        | 2.2.2. Formal Problem Statement                                                                                     | 28           |

|        | 2.2.3. Complexity                                                                                                   | 29           |

|        | 2.2.4. Results and Solution Approaches                                                                              | 29           |

|        |                                                                                                                     |              |

|        | 2.2.5.  | Motivation for a New Integer Programming Approach                            | 31 |

|--------|---------|------------------------------------------------------------------------------|----|

| 2.3.   | Basic ( | Concepts and Notations                                                       | 32 |

|        | 2.3.1.  | Predecessors, Successors, Independence                                       | 32 |

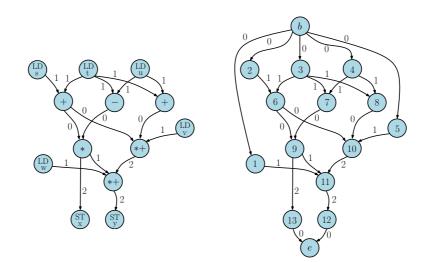

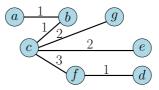

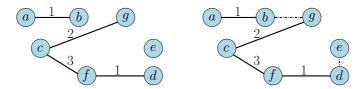

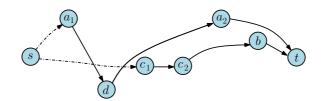

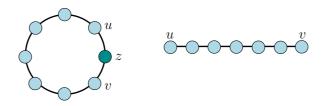

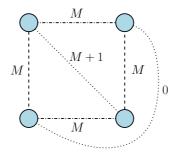

|        | 2.3.2.  | Data-Dependency Graphs                                                       | 32 |

|        | 2.3.3.  | Definitions Related to Lower and Upper Bounds $\ldots \ldots$                | 35 |

| 2.4.   | Search  | Space Reduction Techniques                                                   | 35 |

|        | 2.4.1.  | Global Upper Bounds                                                          | 36 |

|        | 2.4.2.  | Global Lower Bounds                                                          | 40 |

|        | 2.4.3.  | Improving Bounds on Issue Cycles and Distances                               | 45 |

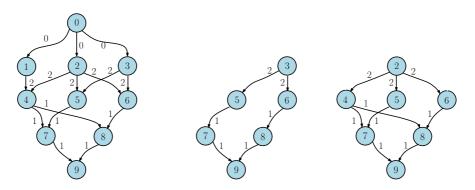

|        | 2.4.4.  | Obtaining New Precedences by DAG Transformations $\ . \ . \ .$               | 49 |

|        | 2.4.5.  | New Ideas to Reduce the Search Space and Break Symmetries                    | 50 |

| 2.5.   | A Nov   | el Efficient Precedence Data Structure                                       | 53 |

| Chapte |         | Novel Integer Programming Approaches to Sequential<br>Instruction Scheduling | 57 |

| 3.1.   | The M   | ain Challenge in Mathematically Modeling Sequential Schedules                | 58 |

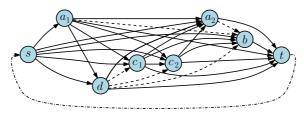

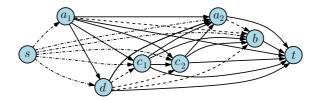

| 3.2.   | The Li  | near Ordering Problem                                                        | 61 |

|        | 3.2.1.  | Formal Definition                                                            | 61 |

|        | 3.2.2.  | Mathematical Formulation                                                     | 61 |

|        | 3.2.3.  | Projection                                                                   | 63 |

|        | 3.2.4.  | The Linear Ordering Polytope                                                 | 63 |

| 3.3.   | Schedu  | lling and Linear Ordering                                                    | 65 |

|        | 3.3.1.  | Single Machine Scheduling and Linear Ordering                                | 65 |

|        | 3.3.2.  | An Interesting Relation To Parallel Machine Problems                         | 67 |

|        | 3.3.3.  | Single-Issue Instruction Scheduling by Linear Ordering                       | 67 |

| 3.4.   | Novel   | Linear Ordering Formulations for Instruction Scheduling $\ldots$             | 69 |

|        | 3.4.1.  | Modeling Preliminaries                                                       | 69 |

|        | 3.4.2.  | Modeling Distances and Betweenness                                           | 69 |

|        | 3.4.3.  | Lower and Upper Bound Constraints                                            | 71 |

|        | 3.4.4.  | Improved Distance Constraints                                                | 72 |

|        | 3.4.5.  | Modeling Idle Cycles                                                         | 74 |

|        | 3.4.6.  | First Model with General Integer NOP Variables $\ . \ . \ .$ .               | 75 |

|        | 3.4.7.  | Second Model with General Integer NOP Variables                              | 77 |

|        | 3.4.8.  | Third Model with NOPs Being Artificial Instructions                          | 79 |

|        | 3.4.9.  | A Short Comparison of the Models                                             | 80 |

| 3.5.   | Additi  | onal New Classes of Inequalities                                             | 80 |

|                              | 3.5.1.                                                                                                           | Conditional Issue Cycle Bound Constraints                       | 80                                                                                      |

|------------------------------|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------|

|                              | 3.5.2.                                                                                                           | Transitivity-driven Conditional Bound Constraints $\ldots$ .    | 84                                                                                      |

|                              | 3.5.3.                                                                                                           | Conditional NOP Constraints                                     | 85                                                                                      |

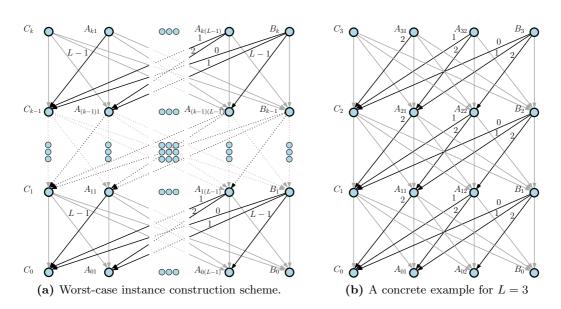

|                              | 3.5.4.                                                                                                           | Gap Filling cuts                                                | 86                                                                                      |

|                              | 3.5.5.                                                                                                           | Interval Filling Cuts                                           | 91                                                                                      |

|                              | 3.5.6.                                                                                                           | Predecessor / Successor Set Constraints                         | 93                                                                                      |

|                              | 3.5.7.                                                                                                           | Superiority Inequalities                                        | 93                                                                                      |

|                              | 3.5.8.                                                                                                           | Variable Equality Constraints                                   | 94                                                                                      |

|                              | 3.5.9.                                                                                                           | NOP Difference Constraints                                      | 94                                                                                      |

| 3.6.                         | The B                                                                                                            | ranch-and-Cut Implementation                                    | 95                                                                                      |

|                              | 3.6.1.                                                                                                           | Formulation as a Feasibility Problem                            | 95                                                                                      |

|                              | 3.6.2.                                                                                                           | Branching Rules                                                 | 96                                                                                      |

|                              | 3.6.3.                                                                                                           | Propagation at Subproblems                                      | 97                                                                                      |

|                              | 3.6.4.                                                                                                           | A Primal Heuristic Based on List Scheduling $\ . \ . \ . \ .$ . | 97                                                                                      |

|                              | 3.6.5.                                                                                                           | Cutting Plane Separation Strategy                               | 98                                                                                      |

|                              | 3.6.6.                                                                                                           | Implementation with ABACUS                                      | 99                                                                                      |

| 3.7.                         | Exper                                                                                                            | imental Evaluation                                              | 100                                                                                     |

|                              | 4                                                                                                                |                                                                 | 107                                                                                     |

| Chapte                       | er 4                                                                                                             | Offset Assignment                                               | 107                                                                                     |

| <b>Chapte</b><br>4.1.        |                                                                                                                  |                                                                 | 107                                                                                     |

| -                            | Motiva                                                                                                           | -                                                               |                                                                                         |

| 4.1.                         | Motiva<br>Proble                                                                                                 | ation                                                           | 108                                                                                     |

| 4.1.<br>4.2.                 | Motiva<br>Proble                                                                                                 | ation                                                           | 108<br>111                                                                              |

| 4.1.<br>4.2.                 | Motiva<br>Proble<br>Model                                                                                        | ation                                                           | 108<br>111<br>113                                                                       |

| 4.1.<br>4.2.                 | Motiva<br>Proble<br>Model<br>4.3.1.<br>4.3.2.                                                                    | ation                                                           | 108<br>111<br>113<br>114                                                                |

| 4.1.<br>4.2.<br>4.3.         | Motiva<br>Proble<br>Model<br>4.3.1.<br>4.3.2.<br>Optim                                                           | ation                                                           | 108<br>111<br>113<br>114<br>116                                                         |

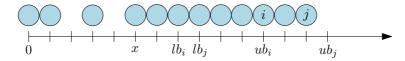

| 4.1.<br>4.2.<br>4.3.         | Motiva<br>Proble<br>Model<br>4.3.1.<br>4.3.2.<br>Optim                                                           | ation                                                           | 108<br>111<br>113<br>114<br>116<br>116                                                  |

| 4.1.<br>4.2.<br>4.3.         | Motiva<br>Proble<br>Model<br>4.3.1.<br>4.3.2.<br>Optim<br>4.4.1.                                                 | ation                                                           | 108<br>111<br>113<br>114<br>116<br>116<br>117                                           |

| 4.1.<br>4.2.<br>4.3.         | Motiva<br>Proble<br>Model<br>4.3.1.<br>4.3.2.<br>Optim<br>4.4.1.<br>4.4.2.                                       | ation                                                           | 108<br>111<br>113<br>114<br>116<br>116<br>117<br>118                                    |

| 4.1.<br>4.2.<br>4.3.         | Motiva<br>Proble<br>Model<br>4.3.1.<br>4.3.2.<br>Optim<br>4.4.1.<br>4.4.2.<br>4.4.3.<br>4.4.3.<br>4.4.4.         | ation                                                           | 108<br>111<br>113<br>114<br>116<br>116<br>117<br>118<br>120                             |

| 4.1.<br>4.2.<br>4.3.<br>4.4. | Motiva<br>Proble<br>Model<br>4.3.1.<br>4.3.2.<br>Optim<br>4.4.1.<br>4.4.2.<br>4.4.3.<br>4.4.4.<br><b>er 5</b>    | ation                                                           | 108<br>111<br>113<br>114<br>116<br>116<br>117<br>118<br>120<br>120                      |

| 4.1.<br>4.2.<br>4.3.<br>4.4. | Motiva<br>Proble<br>Model<br>4.3.1.<br>4.3.2.<br>Optim<br>4.4.1.<br>4.4.2.<br>4.4.3.<br>4.4.4.<br><b>er 5</b>    | ation                                                           | 108<br>111<br>113<br>114<br>116<br>116<br>117<br>118<br>120<br>120<br><b>121</b>        |

| 4.1.<br>4.2.<br>4.3.<br>4.4. | Motiva<br>Proble<br>Model<br>4.3.1.<br>4.3.2.<br>Optim<br>4.4.1.<br>4.4.2.<br>4.4.3.<br>4.4.4.<br>er 5<br>Simple | ation                                                           | 108<br>111<br>113<br>114<br>116<br>116<br>117<br>118<br>120<br>120<br><b>121</b><br>122 |

|      | 5.2.1. | Models Supporting Autoin-/decrement Instructions   | 127 |

|------|--------|----------------------------------------------------|-----|

|      | 5.2.2. | Models Supporting General Auto-Modify Instructions | 130 |

| 5.3. | Brancl | h-and-Cut Implementations                          | 133 |

|      | 5.3.1. | Cutting Plane Generation                           | 134 |

|      | 5.3.2. | Primal Heuristics                                  | 134 |

| 5.4. | Heuris | tics                                               | 134 |

| 5.5. | Experi | imental Results                                    | 136 |

|      | 5.5.1. | OffsetStone                                        | 136 |

|      | 5.5.2. | Test System                                        | 136 |

|      | 5.5.3. | Min-Cost Flow Implementation                       | 137 |

|      | 5.5.4. | Simple Offset Assignment                           | 138 |

|      | 5.5.5. | General Offset Assignment                          | 140 |

# Introduction

This thesis deals with the optimal solution of two optimization problems, *instruction* scheduling and offset assignment, that arise in the machine code generation phase of compilers for various processor architectures.

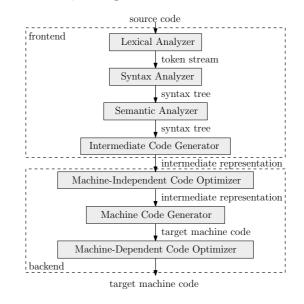

At a high abstraction level, a compiler can be considered to consist of two main components that are respectively called *frontend* and *backend* of the compiler (cf. Fig. 1). Roughly speaking, the frontend takes the input source code, analyzes the control and data flow of the associated program and transforms it into some form of internal representation. The backend then uses this internal representation in order to map the respective operations to machine code instructions of the target architecture and applies several optimizations to it. The two problems addressed in this thesis belong to the machine-dependent code optimizations in the backend part of a compiler. Apart from that, both problems are rather unrelated to each other.

**Figure 1:** A schematic and highly abstracted illustration of the organization of a compiler. It is a close adaptation of an image from [ALSU86].

An instruction scheduler is implemented into almost any compiler irrespective of the target processor architecture. It is responsible for deriving a processing order of the machine code instructions generated in the *instruction selection* phase (and, depending on the implementation, *register allocation* phase) preceding the instruction scheduling step within the backend. Almost all modern processors are *pipelined*. They partition the execution of an instruction into several stages such that a new instruction can enter the first stage while preceding ones are still being processed by the other stages. However, the ideal flow of instructions through the pipeline is harmed by dependencies between instructions on the one hand, and by the varying latencies caused by the processor's functional units and the transmission of data via buses, registers and memory on the other. Functional units realizing more complex instructions need more time in order to make their results available in logic than simpler ones. Some particular operations may even be hard to integrate into the pipeline at all and then need to be synchronized with the flow of pipelined instructions in the case of data dependencies. Further, direct accesses to the main memory may be slower than instructions operating on register values only. A too early insertion of an instruction into the pipeline such that its operands are not yet present in logic when they are needed can be detected by *pipeline interlocks* [HP07]. The pipeline is then stalled for the respective necessary number of clock cycles, effectively prolonging the total execution time. The objective of an instruction scheduler is to avoid such delays caused by pipeline stalls as well as possible. Taking the latencies between dependent instructions into account, an instruction scheduler may reorder the instructions as long as this preserves the semantics of the respective program, i.e., does not violate any data dependencies invoked by the respective computations [ALSU86]. The instruction scheduling phase is therefore a critical step w.r.t. the later runtime performance of a program, especially for *in-order* processors that exactly adhere to the schedule provided by the compiler. Even if a processor is capable of processing instructions *out-of-order*, the runtime performance of a program can be significantly improved by a good or even optimal instruction scheduler.

Offset assignment deals with the placement of variables in memory and with the optimization of accesses to these variables employing the available address registers and specialized addressing instructions provided by the processor. Unlike instruction scheduling, the offset assignment problem occurs mainly in compilers for application-specific processor designs with *Harvard architectures* such as, e.g., digital signal processors. Harvard architectures (in contrast to von Neumann architectures) strictly separate the storage and transmission of instructions and data. Further, special-purpose processors often come with limitations compared to general-purpose processors because they are designed at more restrictive cost conditions or they are subject to hard constraints w.r.t. power dissipation, operating temperature, or size [Mar06]. The processors we are considering for the offset assignment problem have limited addressing capabilities that can lead to a significant overhead in code size and execution time in that additional instructions are necessary to move between the memory locations to be accessed. The overhead can however be at least partially compensated by a smart application of specialized instructions in combination with an optimized memory layout and address register use. This is a typical situation where the reduced complexity of a processor design leads to an increase of complexity on the software side because the generation of efficient machine code becomes much more difficult. In this context, it is worth mentioning some processor design paradigms that will be referred to especially in the context of scheduling. Very long

#### Introduction

instruction word (VLIW) and explicitly parallel instruction computing (EPIC) processors adhere to the idea of moving complexity from hardware to software in an extreme fashion. These design classes rely on compilers to specify complex bundles of instructions to be executed in parallel. On the other hand, the reduced instruction set (RISC, for *reduced instruction set computer*) typically found in applicationspecific processor designs may also simplify some particular tasks of a compiler. For example, register files comprising a comparably large number of general-purpose registers, instruction sets that avoid ambiguity, and a small number of instruction formats can simplify other machine code generation tasks like the already mentioned register allocation and instruction selection phases [ALSU86, HP07].

As indicated, optimizations in the machine code generation phase are crucial for a good runtime performance and also for the size of the resulting programs. Many of them, however, have a high computational complexity which is also true for the two problems dealt with in this thesis. Their  $\mathcal{NP}$ -hardness is the main reason why they are usually solved heuristically in practice, even though this may result in significant performance penalties. On the one hand, it is true that most computer scientists and mathematicians believe that  $\mathcal{P} \neq \mathcal{NP}$  and hence no efficient exact algorithms can be expected for this class of problems. On the other hand, it has been demonstrated several times that the careful adaptation of mathematical optimization techniques to particular problems can permit to compute optimal solutions for instance sizes of practical interest in reasonable time. While it is certainly true that the abstractions used in some 'research problems' can be hard to map to reality and exact approaches are frequently not in a state to be effortlessly used in production compilers, it is sometimes also a matter of missing acceptance if these methods do not find their way to practical use. Nonetheless, the design of exact approaches to compiler optimization problems is being explored by several research groups around the world, not only because optimal solutions are essential in evaluating the quality of heuristics, but also because exact techniques are evolving such that optimal solutions become increasingly achievable. In the domain of technical computer science and engineering, exact algorithms may have even another meaning in answering questions like 'To which extent can the exploitation of a particular feature compensate the lack of another?' as is, e.g., interesting w.r.t. the limited addressing capabilities dealt with in the context of the offset assignment problem. Still the exchange of knowledge between experts in hardware-software co-design, compiler developers and experts in mathematical optimization is improvable. In a way, this thesis aims at being a contribution in this sense, solving problems that the author became aware of when specializing in computer architectures with methods learned when studying mathematical optimization. The main difference of this work to most others in this interdisciplinary field is that the addressed problems are not considered to be 'solved' by mathematically modeling them and then passing them as input to a black-box optimization software. Rather, the combinatorial structure of a problem is investigated and taken into account when designing the respective solution techniques. In particular, existing knowledge about the solution of closely related and well-studied optimization problems, that (partially) characterize the feasible solutions of the problems studied, is exploited in order to implement solvers that remain relatively compact and are able to solve problem instances of medium or even large size. These approaches can as well inspire researchers and practitioners interested in (provably) near-optimal solutions or more sophisticated heuristic and approximation algorithms.

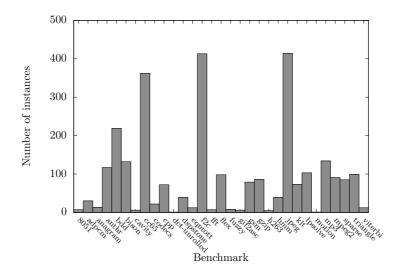

This dissertation starts by establishing the mathematical basis for the applied optimization techniques in the first chapter. The second and third chapters deal with the basic-block instruction scheduling problem for single-issue processors. Basic blocks are program fragments with no side-entrances and -exits, i.e., every instruction of a basic block needs to be executed before the control flow may leave it and enter another basic block. Single-issue processors (ideally) start the execution of exactly one instruction per clock cycle. Chapter 2 introduces the central definitions related to the problem and discusses exact and heuristic solution approaches from the literature. Emphasis is then laid to some more recent preprocessing techniques that permitted to solve large instances to optimality for the first time. In particular, a constraint programming approach that was published in 2006 optimally schedules about 350,000 basic blocks of up to about 2,500 instructions. It was reasonable to suspect that the preprocessing methods can have a positive impact on other solution approaches as well. The last attempt to tackle the problem using integer programming was however not fully equipped with these techniques, and shown not to be competitive to the constraint programming method on the mentioned large benchmark set. Further, the previous integer programming models were almost all based on so-called time-indexed formulations. This was the motivation for a completely different and novel integer programming approach that takes the mentioned preprocessing techniques into account. This approach is the subject of Chapter 3. It is based on *linear ordering variables* and leads to a new characterization of the feasible solutions to the problem. After presenting the models and additional valid inequalities, the corresponding branch-and-cut solver implementation is evaluated using the same test instances that were used for the constraint programming approach. It is capable to solve all but about 150 of the instances to optimality in less than a second of CPU time. There were only eleven instances where it timed out after ten minutes (while only one timed out with the constraint programming solver). The fourth and fifth chapters addressing the offset assignment problem are built up in a similar way. First, Chapter 4 introduces and motivates several variants of the problem, discusses existing approaches as well as known characterizations of the respective sets of feasible solutions, and also some newly developed extensions to these characterizations. Chapter 5 then presents novel integer programming models, starting with the simplest problem variant in which the processor provides only a single address register and very restricted possibilities to avoid address computation overhead. The models are then subsequently extended to deal with multiple address registers and with more flexible addressing capabilities. Finally, the corresponding branch-and-cut solver implementations are evaluated and shown to yield optimal solutions to the majority of about 3,000 real-world instances collected in a standard benchmark set. The results do not only reveal the overhead incurred when using heuristics, but also allow for a first estimation of the impact of the mentioned addressing capabilities on the total address computation overhead.

# Chapter 1

# Preliminaries

This chapter covers the mathematical basics of the problems and solution methodologies discussed and developed in this thesis. The presentation is kept as complete and self-contained as necessary but also as restrictive as possible since it is impossible to investigate these topics as comprehensively as in the vast pertinent literature. The reader interested in a deeper discussion is kindly referred to the textbooks and articles cited in the respective sections. Furthermore, familiarity with the basic concepts of computational complexity, in particular the theory of  $\mathcal{NP}$ -completeness, is assumed.

### 1.1 Combinatorial Optimization

The compiler optimization problems considered in this thesis are particular instances of a general class of *combinatorial optimization problems*. While several differing definitions of combinatorial optimization problems can be found in the literature, we will identify these problems using the common characteristic that their solutions can be expressed as subsets F of a finite ground set  $E = \{e_1, e_2, \dots, e_n\}$  [NW88]. While we call each subset  $F \subseteq E$  a 'solution', we are particularly interested in the set of of *feasible solutions*  $\mathcal{F} = \{F \mid F \subseteq E, F \text{ feasible}\}$ . Further given an objective function  $c: \mathcal{F} \to \mathbb{R}$  such that c(F) denotes the objective function value of each feasible solution  $F \in \mathcal{F}$ , a combinatorial optimization problem Q can be stated as  $Q = (E, \mathcal{F}, c) = \max\{c(F) \mid F \in \mathcal{F}\}$ . This definition naturally covers also minimization problems that can be obtained by simply negating the coefficients of the objective function. As soon as  $\mathcal{F}$  is nonempty, it is clear that the optimum objective function value will be attained by at least one of the feasible solutions since  $\mathcal{F}$  is a finite set [KV12]. Otherwise, we will say that the problem is *infeasible*. Due to its finite nature, a combinatorial optimization problem  $Q = (E, \mathcal{F}, c)$  can in principle be solved by inspection of all possible combinations of elements from E, provided that algorithms to evaluate the feasibility of a solution  $F \subseteq E$  and the objective function value of a feasible solution  $F \in \mathcal{F}$  are available. However, since the number of solutions to inspect is exponential in |E|, such an enumerative approach is intractable for larger problem instances. Even in the frequent case that all the feasible solutions to Q can be constructed in a simple fashion, an enumerative approach may be impractical since also the set  $\mathcal{F}$  may be of exponential size. Taking the simple offset assignment problem, that is addressed in the fourth and fifth chapters of this thesis, as an example, one can consider E to correspond to a set of n program variables and  $\mathcal{F}$  to consist of all linear sequences that can be constructed from them. While the construction of each linear sequence is easy, there are  $\frac{n!}{2}$  of them to evaluate (a sequence and its reverse sequence have the same objective function value). It is however a key observation that an exponential number of feasible solutions does not necessarily mean that the corresponding problem is not polynomial-time solvable. Regardless whether we can expect a polynomial-time algorithm or not, we are interested in approaches that try to avoid the necessity to explicitly consider the entire search space while determining an optimum solution.

In this thesis, we will mainly deal with the special case of *linear combinatorial opti*mization problems where the objective function can be expressed as a linear function  $c: E \to \mathbb{R}$ . Typically, such an objective function assigns costs or weights to each of the elements in E and the value of a solution  $F \subseteq E$  is then simply given by  $c(F) = \sum_{f \in F} c(f)$ . Several problems with varying computational complexity fall into this category. On the one hand, there are instances like the shortest path problem or the maximum spanning tree problem for which polynomial-time combinatorial algorithms exist [CCPS98]. On the other hand, there are (strongly)  $\mathcal{NP}$ -hard problems like the famous traveling salesman problem, the linear ordering problem or the instruction scheduling and offset assignment problems that are all considered in this thesis. For these, there are no polynomial-time algorithms unless  $\mathcal{P} = \mathcal{NP}$ .

## **1.2** (Integer) Linear Programming

Combinatorial optimization problems as just defined usually admit a characterization of their feasible solutions by linear constraints (equations and inequalities) on a number of integral variables and may then be formulated as an *integer (linear) program* (IP)

$$\max \sum_{j=1}^{n} c_j x_j$$

s.t.

$$\sum_{j=1}^{n} a_{ij} x_j \le b_i \qquad \text{for all } i \in \{1, \dots, m\}$$

$$x_j \ge 0 \text{ and integer} \quad \text{for all } j \in \{1, \dots, n\}$$

or max  $\{c^T x \mid Ax \leq b, x \geq 0 \text{ and integer}\}\$  for short [Iba76, Wol98].

Here, A is an  $m \times n$  matrix and b is an m-dimensional column vector,  $c^T$  is an n-dimensional row vector and x is an n-dimensional column vector of unknowns. Since one usually formulates integer programs in order to solve them using a computer, it is reasonable to assume that all the input data is rational, i.e.,  $A \in \mathbb{Q}^{m \times n}$ ,  $b \in \mathbb{Q}^m$ , and  $c \in \mathbb{Q}^n$ . The coefficient matrix A (left hand sides) and the vector of right hand sides b together describe the linear constraints that need to be satisfied by (integral) solutions x, and c imposes the linear objective function on the components of x. As for combinatorial optimization problems, assuming a maximization objective is without loss of generality since a minimization problem can again be obtained by negating the objective function coefficients. The above definition naturally covers also equations

$$\sum_{j=1}^{n} a_{ij} x_j = b_i$$

since these can be represented by the two inequalities

$$\sum_{j=1}^{n} a_{ij} x_j \le b_i \text{ and } \sum_{j=1}^{n} -a_{ij} x_j \le -b_i.$$

Similarly, the trivial inequalities  $x_j \ge 0$  for all  $j \in \{1, \ldots, n\}$  do not impose a true restriction since a general variable  $x'_j$  can be modeled by constraining it to be the difference of two nonnegative variables, i.e.,  $y - z = x'_j$  with  $y, z \ge 0$ .

Solving integer programs is  $\mathcal{NP}$ -hard in general [NW88] and the special case of  $\{0, 1\}$ -IPs where each variable  $x_j$  is restricted to be either zero or one is among Karp's compilation of 21  $\mathcal{NP}$ -hard problems [Kar72]. If the integrality restriction is imposed only on some of the variables, then the formulation is called a *mixed-integer (linear) program* (MIP) and solving it remains, in general,  $\mathcal{NP}$ -hard [NW88]. Finally, if there is no integrality restriction at all, then we are given a *linear program* (LP) that can be solved in polynomial time [Kha79, GL81, Kar84].

Throughout this thesis, we will use the following terminology w.r.t. (integer) linear programs. A vector  $x^* \in \mathbb{R}^n$ ,  $x \ge 0$ , with at least one component  $x_i^* \notin \mathbb{N}_0$  will be

referred to as being fractional. If  $Ax^* \leq b$  holds, then  $x^*$  will be called a fractional solution. For any vector  $x^* \in \mathbb{R}^n$ , irrespective whether fractional or integral, the inequality  $\sum_{j=1}^n a_{ij}x_j \leq b_i$  is said to be satisfied (by  $x^*$ ), if  $\sum_{j=1}^n a_{ij}x_j^* \leq b_i$ . Further, we call the inequality binding (at  $x^*$ ), if it holds that  $\sum_{j=1}^n a_{ij}x_j^* = b_i$ . Finally, we say that the inequality is violated (by  $x^*$ ) if  $\sum_{j=1}^n a_{ij}x_j^* > b_i$ .

### 1.3 Relaxations

Given some optimization problem Q, a relaxation R of Q is another optimization problem that has a potentially larger solution space than Q while every solution to Q is feasible for R as well. Hence, for a maximization problem, if  $z^*$  is the value of an optimum solution to Q, then an optimum solution  $z_R^*$  to R must have an objective function value  $z_R^* \ge z^*$ . In other words,  $z_R^*$  provides an upper bound on the value  $z^*$ of interest. This is useful, e.g., to evaluate the quality of a known feasible solution to problem Q. In particular, if  $z_R^*$  coincides with the objective function value of the known solution, then it is proven to be optimal for Q. A relaxation can therefore help to solve the original problem to optimality in an indirect way, for instance by proving a solution to be optimal that has been obtained heuristically.

In the finite context of combinatorial optimization problems, we can describe relaxations as follows. Let  $Q = (E, \mathcal{F}, c)$  be the original problem and let  $z^* = \max\{c(F) \mid F \in \mathcal{F}\}$  be its optimal objective function value. Then a problem  $R = (E, \mathcal{F}', c)$  is a relaxation of Q if  $\mathcal{F} \subseteq \mathcal{F}'$  and  $z^* \leq \max\{c(F) \mid F \in \mathcal{F}'\}$  [NW88].

Another form of relaxation that we will frequently deal with is a linear program that is derived from an IP (or a MIP) by neglecting any integrality restriction on the variables  $x_j$ ,  $j \in \{1, ..., n\}$ . It is called the *linear programming relaxation* of the respective program. A linear programming relaxation is a *continuous* relaxation since the set of integer feasible solutions is augmented by all solutions  $x \in \mathbb{R}^n$ ,  $x \ge 0$ , with fractional components satisfying the inequality system  $Ax \le b$ . Moreover, we will see in Sect. 1.4.3 that even the solution sets associated to integer programs need not necessarily be finite. Regardless of that, a linear programming relaxation is a true relaxation since we have that

$$z_{LP}^{*} = \max\{c^{T}x \mid Ax \le b, x \ge 0, x \in \mathbb{R}^{n}\} \ge \max\{c^{T}x \mid Ax \le b, x \ge 0, x \in \mathbb{N}_{0}^{n}\} = z^{*}$$

For a particular optimization problem Q, the maximum quotient  $z_{LP}^*/z^*$  that can be attained for any instance of Q is called the *integrality gap* of the LP relaxation.

### **1.4** Linear Programming and Polyhedral Theory

A considerable part of the practical success of linear and integer linear programming techniques stems from investigations of the solution sets associated to the respective problem formulations. Before we dive into this topic in more detail, we need some basic concepts from linear algebra. The following descriptions and results are based on the presentations by Grötschel and Padberg [GP85], Schrijver [Sch86], and Nemhauser and Wolsey [NW88]. Most of the results are restated without their associated proofs that can also be found in the cited references.

#### 1.4.1 Combinations and Independence of Vectors, Convexity

Let  $k, n \in \mathbb{N}$  such that  $k \leq n$ . Consider k vectors  $x^1, \ldots, x^k \in \mathbb{R}^n$  and k scalars  $\lambda_1, \ldots, \lambda_k \in \mathbb{R}$ . A vector  $x \in \mathbb{R}^n$  that can be written as  $x = \lambda_1 x^1 + \cdots + \lambda_k x^k$  is called a *linear combination* of the vectors  $x^1, \ldots, x^k \in \mathbb{R}^n$ . If the additional restriction  $\sum_{i=1}^k \lambda_i = 1$  holds, then x is called an *affine combination* of these vectors.

Closely related to these definitions are the following notions of *independence*. If the only linear combination satisfying the equation  $0 = \lambda_1 x^1 + \cdots + \lambda_k x^k$  has  $\lambda_i = 0$  for all  $i \in \{1, \ldots, k\}$ , then the vectors are said to be *linearly independent*. In any other case, the vectors  $x^1, \ldots, x^k \in \mathbb{R}^n$  are called *linearly dependent*. Similarly, we call the vectors  $x^1, \ldots, x^k \in \mathbb{R}^n$  affinely independent if the only solution to  $0 = \lambda_1 x^1 + \cdots + \lambda_k x^k$ ,  $\sum_{i=1}^k \lambda_i = 0$ , has  $\lambda_i = 0$  for all  $i \in \{1, \ldots, k\}$ , and affinely dependent otherwise. We observe that the vectors  $x^1, \ldots, x^k$  are linearly (affinely) independent if and only if none of them can be expressed as a linear (affine) combination of (a subset of) the others.

By definition, any set  $S \subseteq \mathbb{R}^n$  that contains the zero vector is linearly dependent. The maximum number of linearly independent vectors from  $\mathbb{R}^n$  is n, while the maximum number of affinely independent vectors is n+1. In particular, if  $x^1, \ldots, x^k \in \mathbb{R}^n$  are linearly independent, then  $0, x^1, \ldots, x^k \in \mathbb{R}^n$  are affinely independent.

Besides linear and affine combinations, we consider *conic combinations* where  $\lambda_i \geq 0$  for all  $i \in \{1, \ldots, k\}$ . The vector  $x \in \mathbb{R}^n$ ,  $x = \lambda_1 x^1 + \cdots + \lambda_k x^k$  is called a *convex combination* of the vectors  $x^1, \ldots, x^k$  if it is both, an affine and a conic combination. Moreover, we call a set  $S \subseteq \mathbb{R}^n$  convex, if any convex combination of any two points  $x, y \in S, z = \lambda x + (1 - \lambda)y, \lambda \in [0, 1]$ , is again contained in S.

Provided with a set of vectors  $x^1, \ldots, x^k \in \mathbb{R}^n$ , we are particularly interested in the set of points that can be represented by the different forms of combinations of these vectors. The set of all linear combinations of the vectors  $x^1, \ldots, x^k$ ,

$$\ln(\{x^1,\ldots,x^k\}) := \left\{\sum_{i=1}^k \lambda_i x^i \mid \lambda \in \mathbb{R}^k\right\},\,$$

is called their *linear hull*. Especially, if S is a set of n linearly independent vectors in  $\mathbb{R}^n$ , then  $\lim(S) = \mathbb{R}^n$  and S is a *basis* of  $\mathbb{R}^n$ .

The set of all affine combinations of the vectors  $x^1, \ldots, x^k$ ,

aff

$$(\{x^1,\ldots,x^k\}) := \left\{\sum_{i=1}^k \lambda_i x^i \mid \lambda \in \mathbb{R}^k, \sum_{i=1}^k \lambda_i = 1\right\},\$$

is called their affine hull.

Analogously, the set of all conic combinations of the vectors  $x^1, \ldots, x^k$ ,

$$\operatorname{cone}(\{x^1,\ldots,x^k\}) := \left\{\sum_{i=1}^k \lambda_i x^i \mid \lambda \in \mathbb{R}^k, \, \lambda_i \ge 0\right\},\,$$

forms a *cone* or a *conic subspace* in  $\mathbb{R}^n$ .

We will also need the set of all convex combinations of the vectors  $x^1, \ldots, x^k$ ,

$$\operatorname{conv}(\{x^1,\ldots,x^k\}) := \left\{\sum_{i=1}^k \lambda_i x^i \mid \lambda \in \mathbb{R}^k, \, \lambda_i \ge 0 \text{ and } \sum_{i=1}^k \lambda_i = 1\right\},\$$

that is called their *convex hull*.

#### 1.4.2 Rank and Dimension

The rank of a set  $S \subseteq \mathbb{R}^n$ , rank(S), is the maximum number of linearly independent vectors contained in S. Similarly, the *affine rank* of S,  $\operatorname{arank}(S)$ , is the maximum number of affinely independent vectors contained in S. In particular, if the zero vector can be expressed as an affine combination of the vectors in S ( $0 \in \operatorname{aff}(S)$ ), then  $\operatorname{arank}(S) = \operatorname{rank}(S) + 1$ , and  $\operatorname{arank}(S) = \operatorname{rank}(S)$  otherwise. The *dimension*  $\dim(S)$  of S is defined as  $\dim(S) = \operatorname{arank}(S) - 1$ . In case that  $\dim(S) = n$ , then the set S is called *full-dimensional*.

Let  $A \in \mathbb{R}^{m \times n}$  be a matrix. The rank of A is equally given by the maximum number of linearly independent rows or columns of A. If A defines the left hand sides of inequalities or equations, we will sometimes say 'linear independent inequalities (equations)' and mean the linear independence of the vectors given by their associated matrix rows. The linear equation system Ax = b has at least one solution  $x \in \mathbb{R}^n$  if rank $(A) = \operatorname{rank}([A \ b])$  where  $[A \ b]$  is the *augmented matrix* that results when interpreting b as a further column appended to A. In other words, in order for Ax = b to have a solution, the vector b must be expressible as a linear combination of the columns of A. In particular, Ax = b has a unique solution  $x^*$  if rank $(A) = \operatorname{rank}([A \ b]) = n$ .

#### 1.4.3 Polyhedra

The following definition of a *polyhedron* combines those given in [GP85] and [NW88].

**Definition 1.4.1.** (Polyhedron, Polytope [GP85, NW88]). A set  $P \subseteq \mathbb{R}^n$  is called a polyhedron, if there exists an  $m \in \mathbb{Z}_{\geq 0}$ , a matrix  $A \in \mathbb{R}^{m \times n}$  and a vector  $b \in \mathbb{R}^m$ such that  $P = \{x \in \mathbb{R}^n \mid Ax \leq b\}$ . A polyhedron P is also called a polytope if it is bounded, i.e., if there exists a scalar  $w \in \mathbb{R}$ ,  $w \geq 0$ , such that  $P \subseteq \{x \in \mathbb{R}^n \mid -w \leq x_i \leq w \text{ for all } i \in \{1, \ldots, n\}\}$ .

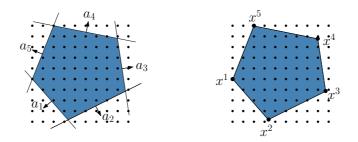

Comparing this definition with the one given for linear programs in Sect. 1.4, it can be seen directly that the solution set described by the inequalities of an LP is a polyhedron and that the solution set of the associated IP consists of the integral points contained in it. This is depicted in the left picture of Fig. 1.1 for the case of a two-dimensional polytope. Classical results by Minkowski [Min96] and Weyl [Wey35] state that any polyhedron has a second characterization besides the one by linear inequalities. If a polyhedron  $P = \{x \in \mathbb{R}^n \mid Ax \leq b\}$  is not bounded, then there are vectors  $r \in \mathbb{R}^n$  such that  $x + \lambda r \in P$  for all  $x \in P$  and  $\lambda \geq 1$ . The vectors r represent an *unbounded direction* of P and are also called *rays* of P. Moreover, the finite set

**Figure 1.1:** A two-dimensional polytope defined by inequalities  $a_i^T x \leq b_i$  (left) and as the convex hull of extreme points  $x^1, \ldots, x^5 \in \mathbb{R}^2$  (right).

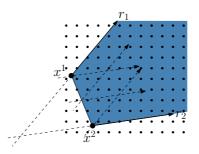

$R = \{r^1, \ldots, r^l\}$  of P's rays that cannot be expressed as a convex combination of any other rays are called P's extreme rays. The mentioned classical results state that Pcan then be expressed by the Minkowski sum of the convex sets given by all convex combinations of its extreme points  $\{x^1, \ldots, x^k\}$  and all conic combinations of its extreme rays  $\{r^1, ..., r^l\}$ , i.e.,  $P = \text{conv}\{x^1, ..., x^k\} + \text{cone}\{r^1, ..., r^l\}$  (cf. Fig. 1.2). Here, the Minkowski sum of two sets  $X, Y \subseteq \mathbb{R}^n$  is defined as  $X + Y = \{x + y \mid x \in \mathbb{R}^n \}$  $x \in X, y \in Y$ . If P is a polytope, the conic part is not needed and P can be expressed as the convex hull of its extreme points only, as is depicted in the right picture of Fig. 1.1. While it is possible to transform a polyhedral description by linear inequalities into a description by extreme points (and extreme rays), this is usually an expensive operation. Any extreme point of  $P = \{x \in \mathbb{R}^n \mid Ax \leq b\}$ is given by the intersection of n linearly independent inequalities. Consequently, if the matrix A has m rows, then P can have up to  $\binom{m}{n}$  extreme points. Hence, it is possible that the description by extreme points has a size that is exponential in n. Moreover, the number m of inequalities necessary to completely describe P can itself be already exponential in n.

**Figure 1.2:** A polyhedron defined by the extreme points  $x^1, x^2 \in \mathbb{R}^2$  and the extreme rays  $r_1, r_2 \in \mathbb{R}^2$ . The dashed lines indicate how the Minkowski sum translates the cone spanned by  $r_1$  and  $r_2$  onto conv $\{x^1, x^2\}$ , i.e., the line between  $x^1$  and  $x^2$ .

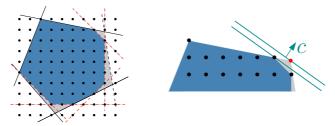

For many polyhedra that are associated with combinatorial optimization problems, no complete description of their feasible region by linear inequalities is known. If it is known though, then the corresponding problem can be solved as a (huge) linear program. In case that the number of the inequalities is polynomial in the input size of the problem, the optimization could then be carried out in polynomial time. However, usually only a problem description is known that defines a polyhedron whose integral points correspond to the set of feasible solutions, but the inequalities do not define the convex hull of these points. In this case, where a problem Qis modeled as an integer program max  $\{c^T x \mid Ax \leq b, x \geq 0, x \in \mathbb{N}_0^n\}$ , i.e., the variables are explicitly constrained to be integer without expressing this in terms of inequalities, often a comparably small number of inequalities suffices in order to characterize the feasible solutions to Q. Still 'comparably small' may mean that the number of necessary constraints is exponential in n. Compare the two polytopes in the left image of Fig. 1.3. Both describe the same set of integer feasible points. However the larger one includes some more fractional points that are exactly cut off by the additional inequalities of the smaller one. Every extreme point of the inner polytope corresponds to an integral feasible solution and lies in the intersection of exactly two inequalities. It can further be observed that the optimal solutions of the inner and outer polytopes do not coincide w.r.t. the example objective function shown in the right picture of Fig. 1.3 that focuses on the upper right corner of the left one.

**Figure 1.3:** Two polytopes with the same set of integral solutions. Only the inner one completely describes their convex hull by linear inequalities. The right image shows an objective function leading to different optima w.r.t. the two polytopes.

#### 1.4.4 Hyperplanes, Faces and Facets

Let  $P = \{x \in \mathbb{R}^n \mid Ax \leq b\}$  be a polyhedron. Consider the *i*-th inequality  $a^T x \leq b_i$ of P. If  $a \neq 0$ , the associated set  $S = \{x \in \mathbb{R}^n \mid a^T x \leq b_i\}$  is called a halfspace since it partitions the  $\mathbb{R}^n$  into the sets of points  $\{x \in \mathbb{R}^n \mid a^T x \leq b_i\}$  (that satisfy the inequality) and  $\{x \in \mathbb{R}^n \mid a^T x > b_i\}$  (that violate the inequality). In particular, provided that the row vectors of A are all nonzero vectors, they define halfspaces and therefore any polyhedron  $P \subsetneq \mathbb{R}^n$  is the intersection of finitely many halfspaces. The boundary  $H = \{x \in \mathbb{R}^n \mid a^T x = b_i\}$  of a halfspace is called a hyperplane.

Of special interest are inequalities whose associated hyperplanes provide a good characterization of the solutions to a certain problem. An inequality  $a^T x \leq b_i$  is called *valid* w.r.t. to a polyhedron P if  $P \subseteq \{x \in \mathbb{R}^n \mid a^T x \leq b_i\}$ . The associated hyperplane  $H = \{x \in \mathbb{R}^n \mid a^T x = b_i\}$  is called a *supporting hyperplane* if  $P \cap H$  is nonempty or, equivalently, if max  $\{a^T x \mid x \in P\} = b_i$ . The intersection of P with a (supporting) hyperplane H is called a *face* of P. We then say that the face Fis defined (or induced) by the inequality  $a^T x \leq b_i$  associated to the hyperplane H. A face F is a proper face of P if  $F \neq P$  and a nontrivial face of P if F is proper and nonempty. Of central interest is the dimension  $\dim(F)$  of a face F. It can be shown that if F is a proper face of the polyhedron  $P = \{x \in \mathbb{R}^n \mid Ax \leq b\}$ with A being an  $m \times n$  matrix, then there exists an index set  $R \subseteq \{1, \ldots, m\}$ such that  $F = \{x \in P \mid \sum_{j=1}^n a_{rj}x_j = b_r$  for all  $r \in R\}$  [GP85]. Let  $A_R$  and  $b_R$ be the respective rows of A and b. Then the dimension  $\dim(F)$  of F is given by  $\dim(F) = n - \operatorname{rank}([A_R \ b_R])$  [Sch86]. In particular,  $0 \leq \dim(F) \leq \dim(P) - 1$ . We already came across the zero-dimensional faces of a polyhedron P, called vertices, that are exactly its extreme points. By the above relation, for any vertex  $x^* \in P$ there exists a submatrix  $A_R$  of A consisting of n linearly independent rows such that  $\operatorname{rank}([A_R \ b_R]) = n$  and  $x^* = A_R^{-1}b_R$ . The one-dimensional faces of P are referred to as edges. Moreover, the faces of dimension  $\dim(P) - 1$  are called facets and the inequalities corresponding to their supporting hyperplanes are called facet-inducing. Facet-inducing inequalities are particularly important due to the following theorem that classifies the role of facets in terms of minimal descriptions of polyhedra.

**Theorem 1.4.1.** ([NW88]). Any polyhedron P has a unique (up to scalar multiplication) minimal representation by a finite set of linear equations and inequalities. In particular, for each facet  $F_i$  of P, the minimal representation contains an inequality  $a^T x \leq b_i$  (unique up to scalar multiplication) representing  $F_i$ .

#### 1.4.5 Basic Solutions and the Simplex Algorithm

We want to elaborate on the connection between polyhedra and linear programs in some more detail. Let us recall from Sect. 1.4.4 that, for any vertex  $x^*$  of a polyhedron  $P = \{x \in \mathbb{R}^n \mid Ax \leq b\}$ , there exists a submatrix  $A_R$  consisting of nlinearly independent rows of A so that rank( $[A_R \ b_R]$ ) = n and  $x^* = A_R^{-1} b_R$  is the unique solution to the system  $A_R x = b_R$ . Geometrically,  $x^*$  lies in the intersection of the hyperplanes associated to the n linearly independent rows of A. In the general discussion of polyhedra in Sect. 1.4.3 and Sect. 1.4.4, we did not assume the vectors satisfying the system of inequalities  $Ax \leq b$  to be nonnegative but required the  $m \times n$ matrix A to have rank n which ensures that the associated polyhedron has at least one vertex. Now, we reinstall the nonnegativity property and consider polyhedra of the form  $P = \{x \in \mathbb{R}^n \mid Ax \leq b, x \geq 0\}$  corresponding to the feasible regions of linear programs as defined in Sect. 1.2. In this case, we can sacrifice the rank assumption on A because the trivial inequalities,  $x_j \ge 0$  for all  $j \in \{1, \ldots, n\}$ , are clearly linearly independent. So if rank(A) < n, then P has vertices that lie on some of the axes. For each such vertex  $x^*$ , we may use the corresponding trivial inequalities to build a matrix  $A_R$  such that rank $([A_R b_R]) = n$ . Since the row and column vectors of  $A_R$  form a basis of  $\mathbb{R}^n$ , a vertex solution  $x^*$  that is feasible w.r.t. all the inequalities  $Ax \leq b$  is also called a *basic feasible solution*. In the special case that the feasible region P is empty, we call the associated linear program *infeasible*. Further, if there is an objective function  $c^T x$  such that  $\max\{c^T x \mid x \in \mathbb{R}^n, Ax \leq b, x \geq 0\} = \infty$ , then the associated linear program is unbounded. If a linear program is neither infeasible nor unbounded then there is an optimum solution that will be attained and the following theorem provides us with a useful characterization of LP optima.

**Theorem 1.4.2.** ([NW88]). Let  $P = \{x \in \mathbb{R}^n \mid Ax \leq b, x \geq 0\}$  be a nonempty polyhedron and let  $\max\{c^Tx \mid x \in \mathbb{R}^n, Ax \leq b, x \geq 0\}$  be an objective function that does not correspond to an unbounded direction of P. Then there exists a vertex  $x^* \in P$  such that  $c^Tx^* = \max\{c^Tx \mid x \in \mathbb{R}^n, Ax \leq b, x \geq 0\}$ .

Theorem 1.4.2 gives rise to the well-known simplex algorithm to solve linear programs. The simplex algorithm finds the vertices of P indirectly by considering the possible combinations of (at least) n inequalities (those from A plus the trivial ones) to be satisfied with equality. A first feasible basic solution can be found by solving an auxiliary problem with a modified objective function (and potentially some additional column exchange operations). This is usually referred to as *phase one* of the simplex algorithm. Assuming a maximization problem, the main routine (phase two) of the algorithm starts from a basic feasible solution and then iteratively moves to an adjacent basic feasible solution (another vertex) with a nondecreasing objective function value as long as this is possible. By Theorem 1.4.2, it must eventually find an optimum solution to the linear program. The motion from one basic solution to an adjacent one is carried out by exchanging so-called basic and non-basic variables (within the simplex algorithm, there are more than n variables due to the addition of slack variables in order to turn inequalities into equations). In general, there can be several candidate variables to make (non-)basic at each iteration and the subroutine to decide which one to choose is known as the *pivoting rule*. There is no proof known for any particular pivoting rule that bounds the number of iterations necessary to arrive at an optimum vertex by a polynomial in the size of the input data. However, and even though provably polynomial-time LP methods exist, the simplex algorithm is still frequently used in practice. Some important reasons for this fact are that (i) the number of iterations observed in practice is often small, (ii) solution methods for linear equation systems can be implemented very efficiently, and (iii) particular variants of the simplex algorithms can be easily 'warmstarted' after adding variables or constraints to the linear program [Sch86]. This will be particularly helpful for the techniques discussed in Sect. 1.5. Nonetheless, for various pivoting rules used in practice, worst case instances with an exponential number of vertices traversed have been reported (see, e.g., [Sch86]).

#### 1.4.6 Cutting Planes and their Separation

#### 1.4.6.1 Cutting Planes

Suppose we want to solve the linear program  $\max\{c^T x \mid x \in \mathbb{R}^n, Ax \leq b, x \geq 0\}$ and assume that the number m of constraints (of A's rows) is large. As we already stated, m may be even a number that is exponential in n for some particular integer programming formulations of combinatorial optimization problems. So consider the case where we relax the linear program by neglecting some of its inequalities. In principle, it suffices to keep enough inequalities such that the associated polyhedron is not unbounded w.r.t. the objective function  $c^T x$ . Let  $A^1$  be a matrix that results from removing some of A's rows, let  $b^1$  be the right hand sides corresponding to the rows in  $A^1$  and suppose that we solve the LP max $\{c^T x \mid x \in \mathbb{R}^n, A^1 x \leq b^1, x \geq 0\}$ . Let  $x^*$  be a solution to this relaxed linear program. Then two cases may occur: Either, it also holds that  $Ax^* \leq b$ , i.e., the solution  $x^*$  satisfies the neglected inequalities without having this enforced explicitly. Or, there exists at least one inequality  $\sum_{j=1}^{n} a_{ij}x_j \leq b_i$  such that  $\sum_{j=1}^{n} a_{ij}x_j^* > b_i$ . By subsequently adding the inequality to the relaxed linear program, we know that  $x^*$  cannot be a solution anymore if we resolve it. We also say, that the solution  $x^*$  is *cut off* or *separated* by the inequality and call it a *cutting plane* or shortly a *cut*. By the interleaved solution of linear programs and addition of cutting planes, we will finally arrive at some solution  $x^*$ that is feasible for our original problem, i.e.,  $x^*$  is an optimum solution to the linear program  $\max\{c^T x \mid x \in \mathbb{R}^n, Ax \leq b, x \geq 0\}$ . When using cutting plane algorithms, we hope to arrive at such a solution without the necessity to add all of the initially neglected inequalities. In general, to avoid that LP relaxations become too large, it is also possible to remove some of the separated inequalities that were satisfied with a large slack in the last LPs, i.e., the term  $b_i - \sum_{j=1}^n a_{ij}x_j$  is (comparably) large.

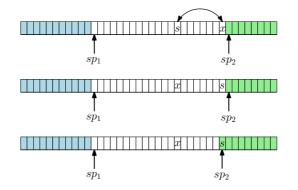

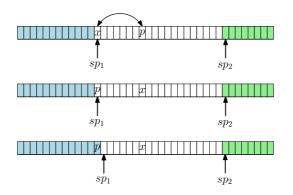

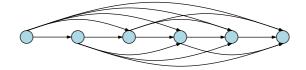

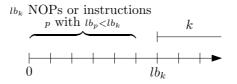

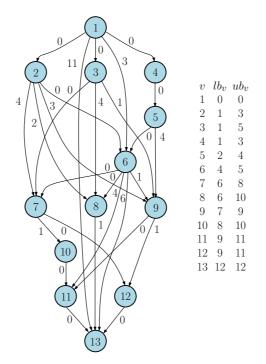

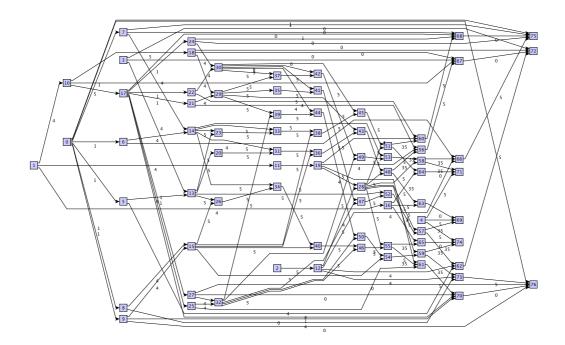

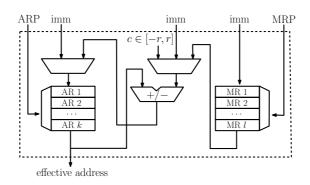

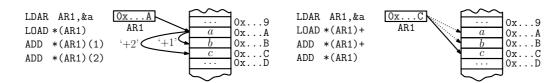

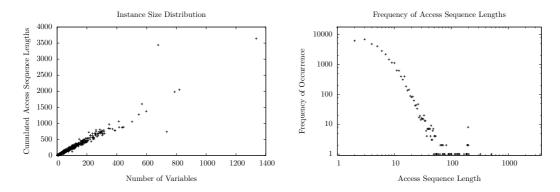

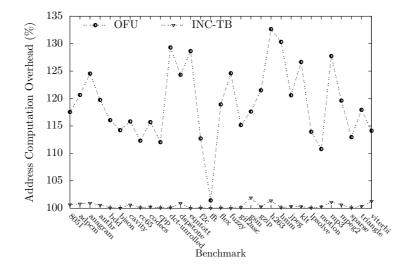

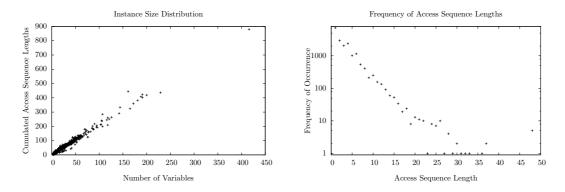

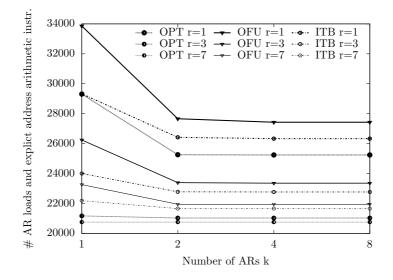

#### 1.4.6.2 Separation